PARALLEL BUS INTERFACE

Specifications

Ajay Chopra

Draft of 2/3/83

#### 1.0 THE PARALLEL BUS INTERFACE (PBI)

The Parallel Bus Interface Connector is a 50-pin connector (See figure 1.0) with the following signals:

PIN 3 through PIN 9 are AO through A6 respectively. PIN 11 through PIN 18 are A7 through A14 respectively. PIN 20 is A15. These are the CPU address lines. The CPU addresses the Parallel Bus Interface devices using these lines.

PIN 21 through PIN 28 are DO through D7 respectively. These are the processor data lines. The CPU transmits and receives data and control information from the Parallel Bus Interface devices on these lines.

PIN 31 is for the Buffered Phase 2 Clock (BO2) Output to the Parallel Bus Interface devices.

PIN 35 is the IRQ (Interrupt Request) input from the Parallel Bus Interface devices. A PBI device can pull this input low to invoke the device handler that services the parallel bus device. This input is "open drain".

PIN 46 is the Latched Read/Write (LR/ $\overline{W}$ ) Output to the Parallel Bus Interface devices. This line is "high" for a read cycle. It is "low" for a write cycle.

PIN 34 is the Reset  $(\overline{POR})$  output to the Parallel Bus Interface devices. This output resets any device so designed on power up and when the RESET key on the CPU keyboard is hit.

PIN 49 is audio in signal from the Parallel Bus devices. This line is connected directly to the audio summation network of the CPU. The audio signal is 1 volt Peak to Peak.

|         | GND      | 1  | 2        | EXT SEL     |                   |

|---------|----------|----|----------|-------------|-------------------|

|         | Α0       | 3  | 4        | A1          |                   |

|         | A2       | 5  | 6        | A3          |                   |

|         | A4       | 7  | 8        | A5          |                   |

| -       | A6       | 9  | 10       | GND         |                   |

|         | A7       | 11 | 12       | А8          |                   |

|         | А9       | 13 | 14       | A1Ø         |                   |

|         | A11      | 15 | 16       | A12         |                   |

|         | A13      | 17 | 18       | A14         |                   |

|         | GND      | 19 | 20       | A15         |                   |

|         | DØ       | 21 | 22       | D1          |                   |

|         | D2       | 23 | 24       | D3          |                   |

|         | D4       | 25 | 26       | D5          |                   |

| CONSOLE | D6       | 27 | 28       | D7          | CONSOLE<br>BOTTOM |

| TOP     | GND      | 29 | 30       | GND         | воттом            |

|         | вØ2      | 31 | 32       | GND         |                   |

|         | Reserved | 33 | 34       | RST         |                   |

|         | ĪRQ      | 35 | 36       | RD <b>Y</b> |                   |

|         | Reserved | 37 | 38       | EXTENB      |                   |

|         | Reserved | 39 | 40       | REF         |                   |

|         | CAS      | 41 | 42       | GND         |                   |

|         | MPD      | 43 | 44       | RAS         |                   |

|         | GND      | 45 | 46<br>48 | lr∕₩        |                   |

|         | Reserved | 47 | 48       | Reserved    |                   |

|         | AUDIO    | 49 | 50       | GND         |                   |

|         | j        |    |          |             |                   |

|         |          |    |          |             |                   |

FIGURE 1.0 PBI CONNECTOR (Looking into the CPU Connector)

PIN 38 is External Decoder Enable (EXTENB) Output. This output goes high when an address on the CPU bus is an allowed address for a PBI device. The CPU generates the EXTENB signal for all segments of the CPU memory map except:

- (a) The Active segments of the O.S. ROM. Any disabled segments of the O.S. ROM generate the EXTENB signal when addressed.

- (b) The region occupied by the internal cartridge (if present).

PIN 2 is the External Select (EXTSEL) Input. This input is generated by the (external) decoder resident in the PBI device. This signal should go low whenever the EXTENB is enabled and the selected PBI device uses the address generated on the CPU Bus. This input is used to disable the CPU decoder for the duration of the current bus cycle.

PIN 36 is the RDY input to the CPU. A slow PBI device can extend the CPU bus cycle by pulling this line low when it is addressed.

PIN 40 is the Refresh (REF) output. This output may be used for the refresh timing of voltile memories connected to the PBI.

PIN 43 is Math Pak Disable (MPD) input from the PBI devices. This input is pulled to the "low" state whenever a Parallel Bus device is selected by the CPU and the device has a handler resident in the region D800H to DFFFH.

PIN 44 is ROW Address Strobe (RAS) output to the Parallel Bus devices. This output may be used for external memory expansion.

PIN 41 is the Column Address Strobe (CAS) output to the Parallel Bus devices. This output may be used for external memory expansion.

PINS 33, 37, 39, 47 and 48 are reserved.

PINS 1, 10, 19, 29, 30, 32, 42, 45 and 50 are Signal grounds (GND).

#### ELECTRICAL LEVELS:

#### D. C. Characteristics

All PBI outputs from the CPU will have the capability of driving one LSTTL gate.

All PBI inputs except IRQ should have the drive capability of the output of an LSTTL gate.

The IRQ input is "open drain" and in the "low" state should present the following characteristics:

V = 0.4V (max) I = 1.6mA (min Sink current)

#### AC Characteristics

To be specified.

# 2.0 Parallel Bus Devices

The Farallel bus will support three types of devices:

### 2.1 External Memory:

The PBI will allow the user to expand the local RAM externally to up to 64K. This will allow external memory expansion of a 16K CPU.

# 2.2 <u>Parallel Bus Peripherals (PBPs)</u>

The PBPs have the following characteristics:

(a) They interface to the CPU through a well defined handler/0.S. interface. The code for this interface is resident in CPU memory location D600H to D7FFH (COMM A & COMM B areas). The ROM containing this code is physically located in a Parallel Bus Adapter. (See Section 3.0)

The O.S. can support up to 8 PBPs at one time.

- (b) Each PBP has a unique handler that resides in the CPU memory space at locations D800H to DFFFH. The ROMs containing the code for these handlers are physically resident in the respective peripherals. (The memory space occupied by the handlers actually contains the Math-pak within the S-16. The Math-pak is disabled whenever any EBP is enabled. See (c) below).

- (c) Location DIFFH in the CPU memory map is reserved for passing control information between the CPU and the PBPs.

The CPU linearly selects the PBI devices by writing into location DIFFH.

| •          | -  | _  |    | . 3 |    |    |    |                 |

|------------|----|----|----|-----|----|----|----|-----------------|

| D <b>7</b> | D6 | D5 | D4 | D3  | D2 | D1 | DØ | Location DIFFH. |

Writing a "1" into Dx (x=0 to 7) selects device Dx (x=0 to 7). Writing a "0" into Dx (x=0 to 7) de-selects device Dx (x=0 to 7).

The CPU can thus select up to 8 PBI devices.

If the  $\overline{\text{IRQ}}$  line is pulled "low" the CPU polls location DIFFH. A read from this location returns the PBI devices' interrupt status.

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| 17 | 16 | 15 | 14 | 13 | 12 | 11 | ΙØ |

### 2.2 Parallel Bus Peripherals (PBPs) (continued)

(c) continued....

If bit Ix (x=0 to 7) is "1", then device Dx (x=0 to 7) has interrupted. If bit Ix (x=0 to 7) is "0" then device Dx (x=0 to 7) has not interrupted. The device is required to clear its interrupt status bit when its interrupt is serviced by the CPU.

- (d) The PBPs should assert MPD only when they are selected.

The PBPs should assert EXTSEL only when they are selected and if EXTENB is asserted.

- (e) The PBPs may respond to any one of the selects Dl through D7. It is recommended that the PBPs have configuration switches to allow them to respond to any one of the selects Dl through D7. The PBPs should not respond to device select DØ. DØ is reserved for use by Atari.

- (f) A peripheral handler may respond to address in the region D800H-DFFH only when it is selected. Location D800H contains the device I.D. of an PBP. If a slot that contains no peripheral is selected, address D800H should return FFH as data.

- (g) A peripheral may respond to addresses in the region D100H to D1FEH only when it is selected.

- (h) The PBPs will have priority over the SIO peripheral when they are addressed generically.

- (i) The data between the CPU and an PBP is passed under the control of the peripheral handler for the PBPs.

- (j) The PBPs will work if a cartridge is present in the cartridge slot.

# 2.3 "External Application" Cartridges:

The External Application Cartridge are a generalization of the PBPs. They have the following characteristics:

- (a) An "External Applications" Cartridge (EAC) can reside at any or all of the addresses in the region 0000H to BFFFH for which the EXTENB is generated. They may respond to these addresses only when "opened."

- (b) The EACs must be "opened" by the S-16 through the slot select location in the same was as the PBPs.

- (c) The EACs must conform to the EXTENB/EXTSEL protocol.

# 2.3 "External Application" Cartridges: (continued)

- (d) The EACs must have a "handler" (resident in locations D800H to DFFFH) that controls their operation. The EACs must conform to conditions (d) thru (g) of Section 2.2 above.

- (e) The EACs will work if a cartridge is present in the internal cartridge slot.

### 3.0 THE PBI ADAPTER CONCEPT:

The use of the PBI shall require a PBI adapter. The PBI adapter shall provide, at a minimum, the following:

- (1) Buffers for the Address, Data, LR/W, BØ2, RAS, CAS, RST, REF and EXTENB Signals.

- (2) 512 bytes of ROM that contain code for the CPU's software interface to the PBPs. This code is resident in locations D600 to D7FF in the CPU memory map. The Adapter will have to decode this address space to generate Chip Select for the ROM.

Any PBI device that does not use the PBI adapter will have to provide (1) above. It will also have to provide (2) above if it is a PBP or an EAC.

The PBI adapter may optionally provide the following in addition to (1) and (2) above:

- (a) RAM memory expansion for a CPU that has less than 64K RAM.

- (b) Device Select address decode (DIFFH and write). This decode may be bussed to the PBI devices connected after the adapter on one of the reserved lines.

- (c) IRQ Status decode (DIFF and read). This decode may be bussed to the PBI devices connected after the adapter on one of the reserved lines.

- (d) Power Supply to support the PBI devices connected to the adapter. Such a power supply may source +5, +12 and -12V. These power signals may be bussed to devices connected after the adapter on reserved lines.

Parallel Bus Interface

Specfications

Steve Miller

4/xx/83

ATARI Company Confidential

#### I. INTRODUCTION

A. References

#### II. BUS DEFINITION

- A. Connector

- B. Signals

#### PARALLEL BUS DEVICES III.

- A. Enternal Memory

- B. Parallel Bus PeripheralsC. External Application Cartridges

#### INTERFACE REQUIREMENTS IV.

- A. D.C. Characteristics

- B. A.C. Characteristics

## I. Introduction

The Parallel Bus Interface (PBI) is method to extend the bus of the ATARI Surely series computers for expansion and enhancement. It will provide a standard interface to peripherals using the expansion box or stand alone unit. This feature will then allow other peripheral manufacturers to design special devices for a limited applications where it would not be profitable for ATARI. Using the PBI as a upgrade path for the smaller computers, the novice can expand their system as their needs grow. An example of this is a ram expansion for the 600 allowing for a full 64K. Due to timing restrictions only one device can be connected to the bus at any one time with the exclusion of the ram module for the 600. Thus to allow for many devices there must be a expansion box.

# A. References

- (1) S-16 Expansion Box Specfication A.Chopra

- (2) Parallel Bus Interface A.Chopra

### II. Bus Definition

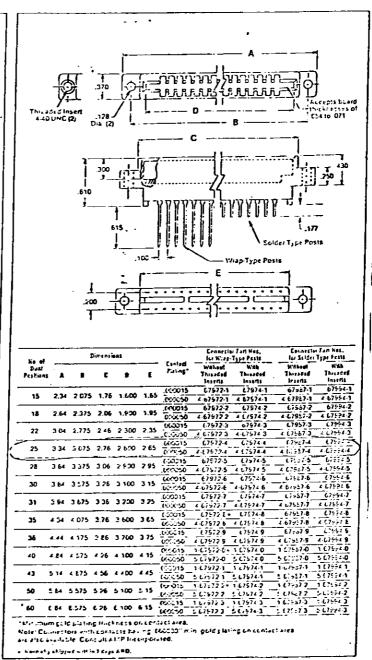

### A. Connector

The PBI signals will be accessible by a 50-pin connection on the computer. This connection consists of a 50-pin, gold plated, card edge (25-pins on each side) with .100 inch centers. It will mate to a standard .100 center 25-dual position circuit connector (i.e. AMP 67987-4) as in figure 1.

Housing Material: Green glass-filled polyester

Contact Material: Copper alloy 725

Contact Finish: Selectively plated fold flash on post for solderability. See table below for plating thickness on contact area. Gold plating per MIL-G<5240, Type II

Replacmant Contacts: .000015" gold plated, Part No. 1-67967-5; .000050" gold plated, Part No. 1-67967-7

Polarizing Keys: Nylon material — Intercontact Type, Part No. 67854-4; 67843

Threaded Insert: Brass, 4:40 UNC

Housing Marking: Marking shown on previous page is standard.

|         |             |    |        | 1               |         |

|---------|-------------|----|--------|-----------------|---------|

|         | GND         | 1  | 2      | EXTSE <b>L'</b> |         |

|         | AO          | 3  | 4      | Al              |         |

|         | A2          | 5  | 6      | A3              |         |

|         | A4          | 7  | 8      | A5              |         |

|         | A6          | 9  | 10     | GND             |         |

|         | A7          | 11 | 12     | A8              |         |

|         | A9          | 13 | 14     | Al0             |         |

|         | A11         | 15 | 16     | A12             |         |

|         | A13         | 17 | 18     | A14             |         |

|         | GND         | 19 | 20     | A15             |         |

|         | D0          | 21 | 22     | Dl              |         |

|         | D <b>2</b>  | 23 | 24     | D3              |         |

|         | D4          | 25 | 26     | D <b>5</b>      |         |

| CONSOLE | D <b>6</b>  | 27 | 28     | D <b>7</b>      | CONSOLE |

| TOP     | GND         | 29 | 30     | GND             | воттом  |

| •       | BO <b>2</b> | 31 | 32     | GND             |         |

|         | Reserved    | 33 | 34     | RST'            |         |

|         | IRQ'        | 35 | 36     | RDY             |         |

|         | Reserved    | 37 | 38     | EXTENB          |         |

|         | Reserved    | 39 | 40     | REF'            |         |

|         | CAS'        | 41 | 42     | GND             |         |

|         | MPD'        | 43 | 44     | RAS'            |         |

|         | GND         | 45 | ··· 46 | LR/W'           |         |

|         | Reserved    | 47 | 48     | Reserved        |         |

|         | AUDIO       | 49 | 50     | GND             |         |

|         |             | -  |        |                 |         |

Figure 2 PBI Connector (Looking into the Computer)

# B. Signals

Shown in figure 2 is the pin-out of the connector looking into the computer. The signal pin numbers and signal names are described below.

| Pin 2  | EXTSEL'         | External Select (Input) ==> collector line is generated the Parallel Bus Device (signal should be active 1 EXTENB is active and the PE and there is a valid PBD active and there is a valid PBD active. EXSEL' causes a CAS' is main board allowing a remaphalthough PBD can be mapped RAM location, these devices the ATARI guidelines for PBS future ATARI devices can be drive device should be capalled. | internally by (PBD). This ow whenever BD is selected ddress on the phing process. in any VALID should follow D locations so e used. The |

|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Pin 3  | AO              | Address Line 0 (Output) ==> 0 is a unbuffered output microprocessor.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |

| Pin 4  | Al <sub>.</sub> | Address Line 1 (Output) ==> 1 is a unbuffered output microprocessor.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |

| Pin 5  | A2              | Address Line 2 (Output) ==> 2 is a unbuffered output microprocessor.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |

| Pin 6  | A3              | Address Line 3 (Output) ==> 3 is a unbuffered output microprocessor.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |

| Pin 7  | A4              | Address Line 4 (Output) ==> 4 is a unbuffered output microprocessor.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |

| Pin 8  | A5              | Address Line 5 (Output) ==> 5 is a unbuffered output microprocessor.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |

| Pin 9  | A6              | Address Line 6 (Output) ==> 6 is a unbuffered output microprocessor.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |

| Pin 11 | A7              | Address Line 7 (Output) ==> 7 is a unbuffered output microprocessor.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |

| Pin 12 | <b>8</b> 4 | Address Line 8 (Output) ==> Address line 8 is a unbuffered output from the microprocessor.                                      |

|--------|------------|---------------------------------------------------------------------------------------------------------------------------------|

| Pin 13 | A9         | Address Line 9 (Output) ==> Address line 9 is a unbuffered output from the microprocessor.                                      |

| Pin 14 | A10        | Address Line 10 (Output) ==> Address line 10 is a unbuffered output from the microprocessor.                                    |

| Pin 15 | All        | Address Line 11 (Output) ==> Address line 11 is a unbuffered output from the microprocessor.                                    |

| Pin 16 | A12        | Address Line 12 (Output) ==> Address line 12 is a unbuffered output from the microprocessor.                                    |

| Pin 17 | A13        | Address Line 13 (Output) ==> Address line 13 is a unbuffered output from the microprocessor.                                    |

| Pin 18 | A14        | Address Line 14 (Output) ==> Address line 14 is a unbuffered output from the microprocessor.                                    |

| Pin 20 | A15        | Address Line 15 (Output) ==> Address line 15 is a unbuffered output from the microprocessor.                                    |

| Pin 21 | D0         | Data Line 0 (Bi-directional) ==> Data line 0 is a buffered line in the 12XX models and unbuffered in the 600 and 800 computers. |

| Pin 22 | D1         | Data Line 1 (Bi-directional) ==> Data line 1 is a buffered line in the 12XX models and unbuffered in the 600 and 800 computers. |

| Pin 23 | D2         | Data Line 2 (Bi-directional) ==> Data line 2 is a buffered line in the 12XX models and unbuffered in the 600 and 800 computers. |

| Pin 24 | D3         | Data Line 3 (Bi-directional) ==> Data line 3 is a buffered line in the 12XX models and unbuffered in the 600 and 800 computers. |

| Pin 25 | D4          | Data Line 4 (Bi-directional) ==> Data line 4 is a buffered line in the 12XX models and unbuffered in the 600 and 800 computers.                                                                                                              |

|--------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 26 | D5          | Data Line 5 (Bi-directional) ==> Data line 5 is a buffered line in the 12XX models and unbuffered in the 600 and 800 computers.                                                                                                              |

| Pin 27 | D <b>6</b>  | Data Line 6 (Bi-directional) ==> Data<br>line 6 is a buffered line in the 12XX<br>models and unbuffered in the 600 and 800<br>computers.                                                                                                     |

| Pin 28 | D <b>7</b>  | Data Line 7 (Bi-directional) ==> Data<br>line 7 is a buffered line in the 12XX<br>models and unbuffered in the 600 and 800<br>computers.                                                                                                     |

| Pin 31 | BO <b>2</b> | Buffered Phase 2 Clock (Output) ==> This clock output line is a buffered phase 2 clock from the processor.                                                                                                                                   |

| Pin 34 | RST'        | Reset (Output) ==> Reset is a active low signal which occurs either on power-up or by depressing the reset key.                                                                                                                              |

| Pin 35 | IRQ'        | Interrupt Request (Input) ==> This open collector line creates a interrupt on the microprocessor. The interrupt can then invoke the handler rom or other service routines for the PBD. The driving device should be capable of sinking 5 mA. |

| Pin 36 | RD <b>Y</b> | Ready (Input) ==> This open collector input signal allows the PBD to halt the microprocessor ONLY during read cycles. This will extend the read cycle for slow peripherals. The driving device should be capable of sinking 5 mA.            |

| Pin 38 | EXTENB      | External Decoder Enable (Output) ==> This output goes high when there is a valid ram access. Any PBD can map during a valid EXTENB but the PBD should only map in according to ATARI specified address locations.                            |

| Pin 40        | REF'  | Refresh (Output) ==>This output can be for refresh timing on voltile memories connected to the PBI.                                                                                                                                                          |

|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin <b>41</b> | CAS!  | Column Address Strobe (Output) ==> This output can be used for access of DRAM external to the computer. Due to timing restrictions caution should be taken when using this signal in the expansion box.                                                      |

| Pin 43        | MPD'  | Math Pack Disable (Input) ==> This open collector input is used to disable the math pack section of the OS rom (D800H-DFFFH). This should be done when the PBD is selected and has a handler resident. The driving device should be capable of sinking 5 mA. |

| Pin <b>44</b> | RAS'  | Row Address Strobe (Output) ==> This output can be used for access of DRAM external to the computer. Due to timing restrictions caution should be taken when using this signal in the expansion box.                                                         |

| Pin 46        | LR/W' | Latched Read Write (Output) ==> This output is active high for a read cycle and active low for a write cycle.                                                                                                                                                |

| Pin 49        | AUDIO | Audio In (Input) ==> This line is tied directly to the audio summation network of the computer. The audio signal input is 1 V peak to peak with 1K ohm input impedance.                                                                                      |

Pins 1,10,19,29,30,32,42,45,50 GND

Pins 33,37,39,47,48

Reserved

## III. Parallel Bus Devices

The PBI is designed to support two types of devices which are the expansion box and external ram for the 600. The expansion box supports both PBD and external application cartridges.

## A. External Ram

The PBI will allow the user to expand ram externally up to 64K. This feature can only be used in the 600 since all other units are already equiped with 64K.

# B. Parallel Bus Peripherals (PBP)

The PBPs have the following characteristics:

- 1. The interface between the PBP and the CPU is defined through the handler/OS resident in the OS rom. The OS can support 8 devices at one time with only one enabled at any given interval.

- 2. Every PBP has a unique handler that resides in the CPU memory from D800H-DFFFH. The roms containing the code for these handlers are physically resident on the respective PBPs. To access this handler, the math pack must be disabled with MPD'. When the math pack is disabled (this should happen whenever the PBP is selected and has a external handler) the computer will generate EXTENB for the math pack area. The PBP must the generate the correct EXTENB EXTSEL' protocol. If the device does not generate EXTSEL' the CPU will access (in the 64K computers) a unused area of ram. This area should not be used since all computers of this series do not have that area of ram.

- 3. The location DIFFH in the CPU memory map is reserved for passing control information between the CPU and the PBPs. The CPU selects one of the PBP devices by writing a "1" into the desired bit in location DIFFH. The device can be deselected by writing a "0" into the desired bit.

| 7        | 6          | 5        | 4            | 3         | 2  | 1            | 0  | _ |

|----------|------------|----------|--------------|-----------|----|--------------|----|---|

| <br>  D7 | D <b>6</b> | <br>  D5 | <br>  D4<br> | l<br>l D3 | D2 | <br>  D1<br> | D0 | ] |

Therefore the CPU can then access 8 devices, one at a time.

#### 3. continued.....

If the IRQ' line is pulled "low" the cpu can read the status for location DIFFH and locate the requesting PBP. A "l" in a bit Ix (where x=0 to 7) corresponds to a interrupt in PBP x. If the bit is a "0" then the device has not caused the interrupt. The PBP must clear the interrupt flag when the interrupt is being serviced.

| 7      | 6  | 5  | 4  | 3  | 2  | 1   | 0  |

|--------|----|----|----|----|----|-----|----|

| İ 17 İ | 16 | I5 | T4 | Т3 | 12 | T 1 | 10 |

- 4. The PBP should assert MPD' only when they are selected. The PBP should assert EXTSEL' only when they are selected and if EXTENB is asserted.

- 5. The PBP may respond to any of the selects any one of the selects DO through D7. It is recommened that the PBPs have configuration switches to allow them to respond to any one of the selects. Some of the systems use the PBI to support internal devices therefore the user should check their manual for device locations. If the system has devices in specific location those are reserved in that computer.

- 6. A peripheral handler may respond to address in the region D800H-DFFFH only when it is selected. The location D800H contains the device I.D. of the PBP.

- 7. A peripheral may respond to address in the region D100H to D1FEH only when selected.

- 8. The PBP will have priority over the SIO peripheral when they are address generically.

- 9. The data between the CPU and the PBP is passed under the control of the peripheral handler for the PBPs.

- 10. The PBPs will work if a cartridge is present in the cartridge slot.

11. The CPU address space from D600H to D7FFH is reserved for PBI devices as follows:

| Device     | Range               | Size     |

|------------|---------------------|----------|

| D0         | D600H-D61FH         | 32 Bytes |

| D1         | D620H-D63FH         | 32 Bytes |

| D <b>2</b> | D640H-D65FH         | 32 Bytes |

| D3         | D6 <b>60H-D67FH</b> | 32 Bytes |

| D4         | D680H-D69FH         | 32 Bytes |

| D5         | D6A0H-D6BFH         | 32 Bytes |

| D <b>6</b> | D6COH-D6DFH         | 32 Bytes |

| D <b>7</b> | D6EOH-D6FFH         | 32 Bytes |

The region from D700H to D7FF is reserved for use by ATARI. The CPU address space from D600H to D7FFH is always mapped to the PBI and does not require the EXTENB|EXTSEL' protocol. Some units may have devices mapped on the PBI, these devices are only active when selected but care must be taken when using using a unit with onboard devices.

# C. External Application Cartridges

The "External Application Cartridge" (EAC) is a generalization of the PBP. They have the following characteristics:

- 1. An EAC can reside at any or all of the locations in the region 0000H to BFFFH for which the EXTENB is generated. They may respond to these address only when "opened".

- 2. The EACs must be opened by the protocol given for the PBPs.

- 3. The EACs must conform to the EXTENB EXTSEL' protocol.

- 4. The EACs must have a handler (resident at location D800H-DFFFH) that controls their operation. The EACs must conform to the conditions (4) through (11) of section III. B. above.

- 5. The EACs will work if a cartridge is present in the internal cartridge slot.

# IV. Interface Requirements

For peripherals to interface through the PBI to the computer the following requirements must be followed.

# A. D.C. Characteristics

All PBI outputs from the CPU have the capability of driving ONE LSTTL load.

All PBI open collector input lines must be able to sink 5 mA (min) at .4 V(max).

All PBI non-open collector input lines execpt AUDIO must have the drive capability of one LSTTL gate.

All PBI signals except AUDIO will be at standard TTL logic levels.

The AUDIO input line must drive a 1K Ohm input impedance with a 1V peak to peak signal.

# B. A.C. Characteristics

Given in Figure 3 are the worst case timing requirements for the PBI.

| Symbol                      | Min | <u>Max</u>  | Units                   | Description               |

|-----------------------------|-----|-------------|-------------------------|---------------------------|

| <sup>T</sup> CYC            |     |             | nS                      | Clk period                |

| т <sub>о2Н</sub>            | 219 | 297         | nS                      | Phase 2 duty cycle        |

| TADS                        |     | 145         | nS                      | Address setup             |

| T <sub>ADH</sub>            | 10  |             | nS                      | Address hold              |

| T <sub>XNS</sub>            |     | 215         | ns                      | EXTENB setup              |

| TXNH                        | 15  |             | nS                      | EXTENB hold               |

| T <sub>XSS</sub>            |     | 253         | nS                      | EXTSEL' setup             |

| TXSH                        | 100 |             | nS                      | EXTSEL' hold              |

| T <sub>DIS</sub>            | 62  |             | n <b>S</b>              | Data in setup             |

| $\mathbf{T}_{\mathtt{DIH}}$ | 10  |             | nS                      | Data in hold              |

| T <sub>DOS</sub>            |     | 112         | nS                      | Data out setup            |

| <br>$\mathbf{T}_{DOH}$      | 10  |             | n <b>S</b>              | Data out hold             |

| T <sub>RWS</sub>            |     | 228         | nS                      | 'R/W' setup               |

| ${f T}_{{\sf RWH}}$         | 10  |             | nS                      | R/W' hold                 |

| T <sub>RFS</sub>            |     | 150         | nS                      | Refresh setup             |

| T <sub>RFH</sub>            | 15  |             | nS                      | Refresh hold              |

| TRDS                        | 200 |             | nS                      | Ready setup               |

| T <sub>RSS</sub>            | 187 | 305         | nS                      | RAS' setup                |

| T <sub>RSH</sub>            | 10  |             | nS                      | RAS' hold                 |

| T <sub>CSS</sub> re         | 295 | 38 <b>5</b> | nS                      | CAS' setup on read cycle  |

| T <sub>CSS wr</sub>         | 409 | 52 <b>2</b> | nS                      | CAS' setup on write cycle |

| T <sub>CSH</sub>            | 10  |             | <sup>"</sup> n <b>S</b> | CAS' hold read or write   |

.

£