# Tempest™ Troubleshooting Guide

Complete with Signatures and Memory Map

# **Table of Contents**

| 1 | Memory Map                                                                                                                                                                                                                           | 1                |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2 | Watchdog                                                                                                                                                                                                                             | 2                |

| 3 | Troubleshooting Using the CAT Box  A. CAT Box Preliminary Set-up  B. Address and Data Lines  C. RAM  D. Option Switch Inputs  E. Custom Audio I/O Chips  F. Player input Switches and Encoder Wheel  G. LED and Coin Counter Outputs | 2 2 3 3 . 4 5    |

| 4 | Troubleshooting with Signature Analysis  A. Signature Analysis Set-up  B. Clock and Reset Circuitry  C. Address Lines  D. Address Decoder  E. ROM and Data Lines  F. Math Box                                                        | 6<br>7<br>7<br>8 |

# List of Illustrations

| Figure 2<br>Figure 3 | Memory Map                   | 3 |

|----------------------|------------------------------|---|

| Figure 6             | Analog Vector-Generator Data | c |

# 1 Memory Map

| MEMORY MAP                                                  |                  |        |        |            |          |        |             |             |             |                                                                                                                                                          |

|-------------------------------------------------------------|------------------|--------|--------|------------|----------|--------|-------------|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| HEXA-<br>DECIMAL<br>ADDRESS                                 | R/W              | D7     | D6     | <b>D</b> 5 | DA<br>D4 |        | D2          | D1          | D0          | FUNCTION                                                                                                                                                 |

| 0000-7FFF<br>0800-080F                                      | R/W<br>W         | D      | D      | D          | D        | D<br>D | D<br>D      | D<br>D      | D<br>D      | Program RAM (2K)<br>Color RAM                                                                                                                            |

| 0C00<br>0C00<br>0C00<br>0C00<br>0C00<br>0C00<br>0C00<br>0C0 |                  | םםם    | 0 00   | D<br>D     | D<br>D   | D      | D<br>D      | D<br>D<br>D | מם          | Right Coin Switch Center Coin Switch Left Coin Switch Slam Switch Self-Test Switch Diag. Step Switch HALT 3KHz Option Switch Inputs Option Switch Inputs |

| 2000-2FFF<br>3000-3FFF                                      | R/W<br>R         | D<br>D | D<br>D | D<br>D     | D<br>D   | D<br>D | D<br>D      | D<br>D      | D<br>D      | Vector RAM (4K)<br>Vector ROM (4K)                                                                                                                       |

| 4000<br>4000<br>4000<br>4000<br>4800                        | W<br>W<br>W<br>W |        |        |            | D        | D      |             | D           | D           | Right Coin Counter<br>Center Coin Counter<br>Video Invert X<br>Video Invert Y<br>VG GO                                                                   |

| 5000<br>5800                                                | W<br>W           |        |        |            |          |        |             |             |             | WD CLEAR<br>VG Reset                                                                                                                                     |

| 6000-603F<br>6040<br>6040<br>6050                           | W<br>W<br>R      | D D D  | D<br>D | D<br>D     | D<br>D   | D<br>D | D<br>D      | D<br>D      | D<br>D      | EAROM Write<br>EAROM Control<br>Math Box Status<br>EAROM Read                                                                                            |

| 6060<br>6070<br>6080-609F                                   | R<br>R<br>W      | D<br>D | D<br>D | D<br>D     | D<br>D   | D D D  | D<br>D<br>D | D<br>D<br>D | D<br>D<br>D | Math Box Read<br>Math Box Read<br>Math Box Start                                                                                                         |

| 60C0-60CF<br>60D0-60DF                                      | R/W<br>R/W       | D<br>D | D<br>D | D<br>D     | D<br>D   | D<br>D | D<br>D      | D<br>D      | D           | Custom Audio Chip 1<br>Custom Audio Chip 2                                                                                                               |

| 60E0<br>60E0<br>60E0                                        | R<br>R<br>R      |        |        | ·          |          |        | D           | D           | D           | One Player Start<br>Two Player Start<br>FLIP                                                                                                             |

| 9000-DFFF                                                   | R                | D      | D      | D          | D        | D      | D           | D           | D           | Program ROM (20K)                                                                                                                                        |

Figure 1 Memory Map

# 2 Watchdog

The Watchdog circuit will cause continuous reset pulses to the microprocessor if a problem exists within the microprocessor circuit. If the self-test fails to run, it is a good practice to check the reset line.

RESET-microprocessor input (pin 40). In a properly operating game, reset should occur during power-up or when the reset push button is activated. A pulsing reset line indicates that something is causing the microprocessor to lose its place within its program. Typical causes are:

- 1. Open or shorted address or data bus lines

- 2. Bad microprocessor chip

- 3. Bad bus buffers

- 4. Bad ROM

- 5. Bad RAM

- Any bad input or output that causes an address or data line to be held in a constant high or low state

A pulsing RESET signal indicates a problem exists somewhere within the microprocessor circuitry rather than within either the Math Box or the Analog Vector Generator.

# 3 Troubleshooting

Using the CAT Box

## A. CAT Box Preliminary Set-up

#### 1. Remove:

- The electrical power from the game.

- The wiring harnesses from the game PCBs.

- The main and auxiliary boards from the game cabinet.

- The microprocessor chip C2 from the main PCB.

#### 2. Connect:

- The harnesses from the game to the main and auxiliary boards. (Use extender cables if available.)

- Φ0 and φ2 test points together.

- WD DIS test point to ground.

- The CAT Box flex cable to the main PCB test edge connector.

### 3. Power Up:

- The game.

- The CAT Box.

#### 4. Set CAT Box Switches:

- TESTER SELF-TEST: (OFF)

- ◆ TESTER MODE: R/W̄

- Press TESTER RESET

# B. Address and Data Lines

NOTE: This section assumes that IC F2 is a 74LS245.

- 1. Perform the CAT Box preliminary set-up.

- 2. Connect the DATA PROBE to the CAT Box and the game ground test point.

- 3. TESTER MODE: R/W

- 4. BYTES: 1.

- 5. PULSE MODE: UNLATCHED

- 6. R/W MODE: (OFF)

- Key in address pattern on the keyboard (use AAAA to start)

- 8. Push DATA SET

- 9. Key in data pattern on the key board (use AA to start)

- 10. R/W MÓDE: STATIC

- Probe the IC-pin with the data probe and check for the 1 or 0 LED as indicated in Figure 2. Repeat this step for each address and data line.

- 12. Repeat steps 6-11 using *5555* in step 7 and *55* in step 9.

### Figure 2 Address and Data Lines

| When writing<br>AAAA pattern | Address and data lines | When writing |

|------------------------------|------------------------|--------------|

| •                            |                        | 5555 pattern |

| Logic State                  | IC-Pin                 | Logic State  |

| 1                            | B3-1                   | 0            |

| 0                            | B3-3                   | 1            |

| 1                            | B3-2                   | 0            |

| 0                            | A/B-3                  | 1            |

| 1_                           | A/B-18                 | 0            |

| 0                            | A/B-16                 | 1            |

| 1                            | A/B-14                 | 0            |

| 0                            | A/B-12                 | 1            |

| 1                            | B/C-3                  | 0            |

| 0                            | B/C-5                  | 1            |

| 1<br>0                       | B/C-7<br>B/C-9         | 0<br>1       |

|                              |                        |              |

| 1                            | B/C-18                 | 0            |

| 0<br>1                       | B/C-16<br>B/C-14       | 1            |

| Ó                            | B/C-14<br>B/C-12       | 0<br>1       |

|                              |                        |              |

| 1<br>0                       | F2-9<br>F2-8           | 0            |

| 1                            | F2-6<br>F2-7           | 1<br>0       |

| ò                            | F2-6                   | 1            |

| 1                            | F2-5                   |              |

| Ö                            | F2-5<br>F2-4           | 0<br>1       |

| 1                            | F2-3                   | Ó            |

| Ó                            | F2-2                   | 1            |

|                              | . — —                  |              |

## C. RAM

1. Perform the CAT Box preliminary set-up

- 2. Set the CAT Box switches as follows:

- a. Press TESTER RESET

- b. DBUS SOURCE: ADDR

- c. BYTES: 1024

- d. R/W MODE: (OFF)

- e. R/W: WRITE

- f. Enter 0000 on the keypad

- g. Toggle R/W MODE to PULSE and back to (OFF)

- h. R/W: READ

- i. Toggle R/W MODE to PULSE and back to (OFF)

- If the CAT Box reads an address that doesn't compare, the COMPARE ERROR LED lights up, the ADDRESS/SIGNATURE display shows the failing address location, and the ERROR DATA DISPLAY switch is enabled. Using this switch, determine if the error is in the high- or low-order RAM.

- 4. Repeat the test with DBUS SOURCE set to ADDR.

- 5. Repeat steps 2-4, entering 0400 on the keypad (step f).

- Repeat steps 2-4, entering 2000 on the keypad (step f).

- Repeat steps 2-4, entering 2400 on the keypad (step f).

- 8. Repeat steps 2-4, entering 2800 on the keypad (step f).

- 9. Repeat steps 2-4, entering 2C00 on the keypad (step f).

# D. Option Switch Inputs

- 1. Perform the CAT Box preliminary set-up.

- 2. BYTES: 1

- 3. R/W: READ

- 4. R/W MODE: (OFF)

- 5. Key in 0D00

- 6. R/W MODE: STATIC

- Activate the option switches at location N13 while monitoring the DATA DISPLAY. The DATA DISPLAY will change if the switches are operating properly.

- 8. Repeat steps 4-7, entering 0E00 in step 5, and activate switches at location L12.

## E. Custom Audio I/O Chips

NOTE: Unlike previous Atari coin-operated games, Tempest™ has two custom audio I/O chips.

Each must be tested separately.

- 1. Perform the CAT Box preliminary set-up.

- 2. BYTES: 1

- 3. R/W: WRITE

- 4. R/W MODE: (OFF)

- 5. Enter address from Figure 3

- 6. Press DATA SET

- 7. Enter the data from Figure 3

- 8. R/W MODE to PULSE and back to (OFF)

- 9. Repeat steps 5-8 for each address and data, noting the test results.

## Figure 3 Custom Audio I/O Chips

| ADDRESS<br>60CF<br>60CF | <b>DATA</b><br>00<br>03 | TEST RESULTS                                                 | ADDRESS<br>60DF<br>60DF | <b>DATA</b><br>00<br>03 | TEST RESULTS                                           |

|-------------------------|-------------------------|--------------------------------------------------------------|-------------------------|-------------------------|--------------------------------------------------------|

| 60C0                    | 55                      |                                                              | 60D0                    | 55                      |                                                        |

| 60C1                    | AF                      | Custom Audio I/O Chip #1 channel 1 produces pure tone.       | 60D1                    | AF                      | Custom Audio I/O Chip #2 channel 1 produces pure tone. |

| 60C1                    | 00                      | Custom Audio I/O Chip<br>#1 channel 1 off.                   | 60D1                    | 00                      | Custom Audio I/O Chip<br>#2 channel 1 off.             |

| 60C2                    | 55                      |                                                              | 60D2                    | 55                      |                                                        |

| 60C3                    | ĀĒ                      | Custom Audio I/O Chip<br>#1 channel 2 produces<br>pure tone. | 60D3                    | AF                      | Custom Audio I/O Chip #2 channel 2 produces pure tone. |

| 60C3                    | 00                      | Custom Audio I/O Chip<br>#1 channel 2 off.                   | 60D3                    | 00                      | Custom Audio I/O Chip<br>#2 channel 2 off.             |

| 60C4                    | 55                      |                                                              | 60D4                    | 55                      |                                                        |

| 60C5                    | AF                      | Custom Audio I/O Chip<br>#1 channel 3 produces<br>pure tone. | 60D5                    | AF                      | Custom Audio I/O Chip #2 channel 3 produces pure tone. |

| 60C5                    | 00                      | Custom Audio I/O Chip<br>#1 channel 3 off.                   | 60D5                    | 00                      | Custom Audio I/O Chip<br>#2 channel 3 off.             |

| 60C6                    | 55                      |                                                              | 60D6                    | 55                      | <u>.</u>                                               |

| 60C7                    | AF                      | Custom Audio I/O Chip<br>#1 channel 4 produces<br>pure tone. | 60D7                    | AF<br>                  | Custom Audio I/O Chip #2 channel 4 produces pure tone. |

| 60C7                    | 00                      | Custom Audio I/O Chip<br>#1 channel 4 off.                   | 60D7                    | 00                      | Custom Audio I/O Chip<br>#2 channel 4 off.             |

## F. Player Input Switches and Encoder Wheel

- 1. Perform the CAT Box Preliminary Set-up

- 2. DBUS SOURCE to DATA

- 3. BYTES: 256

- 4. R/W: WRITE

- 5. R/W MODE: (OFF)

- 6. Key in 60D0

- 7. Press DATA SET

- 8. Key in 00

- 9. Toggle R/W MODE to PULSE and back to (OFF)

- 10. BYTES: 1

- 11. R/W: READ

- 12. Key in 60D8

- 13. R/W MODE: STATIC

- 14. Pushing the following player input switches should cause the DATA DISPLAY to change: FIRE, SUPERZAPPER, 1-player start and 2-player start. (Also Player-2 FIRE and Player-2 SUPER-ZAPPER in cocktail\* games.)

NOTE: For the encoder wheel, repeat the above instructions keying in 60C0 in step 6 and 60C8 in step 12. Turning the encoder wheel should cause the DATA DISPLAY to change.

## G. LED and Coin Counter Outputs

- 1. Perform the CAT Box Preliminary set-up.

- 2. DBUS SOURCE to DATA

- 3. BYTES: 1

- 4. R/W: WRITE

- 5. R/W MODE: (OFF)

- 6. Key in address from Figure 4

- 7. Press DATA SET

- 8. Key in on or off data from Figure 4

- 9. R/W MODE to STATIC and back to (OFF)

- Repeat steps 6-9 to turn off coin counter solenoids, or to test another address.

If you write data that activates a solenoid, deactivate it by pressing the reset button on the game board or by writing "off" data. If you leave a solenoid activated for more than about 10 seconds it will overheat and may have to be replaced.

# Figure 4 LED and Coin Counter Addresses

| ADDRESS | ON-DATA | OFF-DATA | OUTPUT NAME         |

|---------|---------|----------|---------------------|

| 4000    | 01      | 00       | Right Coin Counter  |

| 4000    | 02      | 00       | Center Coin Counter |

| 4000    | 04      | 00       | Left Coin Counter   |

| 60E0    | FD      | FF       | 1-player start LED  |

| 60E0    | FE      | FF       | 2-player start LED  |

## H. Analog Vector-Generator

#### 1. Test:

- 1. Perform CAT Box preliminary set-up.

- 2. DATA SOURCE: DATA

- 3. R/W: WRITE

- 4. R/W MODE: (OFF)

- Key in address from Figure 5 or press AD DRESS INC.

- 6. Press DATA SET

- 7. Key in data from Figure 5

- 8. Set R/W MODE to PULSE and then to (OFF)

- 9. Repeat steps 5-8 for each address in Figure 5

#### CAUTION

You may damage the circuitry of the X-Y monitor if you key in the VG GO signal without first checking all the addresses and data. Check the data by reading each address location using steps 10-14:

- 10. R/W: READ

- 11. R/W MODE: (OFF)

- 12. Key in address or press ADDRESS INC.

- 13. R/W MODE: PULSE

- 14. Check the data in the DATA DISPLAY against the data in Figure 5

If you are sure the data is correct, proceed to steps 15-19:

- 15. R/W MODE: WRITE

- 16. R/W: (OFF)

- 17. Key in VG GO address (4800 for TEMPESTTM)

- 18. R/W to PULSE and then back to (OFF)

- 19. After writing to the VG GO address, the monitor should show a large plus sign. Failure of the horizontal or vertical circuits shows up as a single line drawn on the monitor. If your monitor does not display a large plus sign, contact Atari Field Service.

<sup>\*</sup>To test player-2 inputs in cocktail games connect IC D6-1 to +5.

Figure 5 Analog Vector-Generator Data

| Address | Data | Address | Data | Address | Data |

|---------|------|---------|------|---------|------|

| 2000    | 40   | 200C    | FF   | 2018    | 00   |

| 2001    | 80   | 200D    | 03   | 2019    | 40   |

| 2002    | 00   | 200E    | 00   | 201A    | 80   |

| 2003    | 70   | 200F    | 62   | 201B    | 00   |

| 2004    | 00   | 2010    | 40   | 201C    | 80   |

| 2005    | 1E   | 2011    | 80   | 201D    | 1F   |

| 2006    | 00   | 2012    | 80   | 201E    | 00   |

| 2007    | 1E   | 2013    | 00   | 201F    | 00   |

| 2008    | 00   | 2014    | 00   | 2020    | FF   |

| 2009    | 60   | 2015    | 00   | 2021    | 40   |

| 200A    | FF   | 2016    | 01   | 2022    | 00   |

| 200B    | 03   | 2017    | 1F   | 2023    | E0   |

# 4 Troubleshooting

## With Signature Analysis

## A. Signature Analysis Set-up

- 1. Perform the CAT Box Preliminary set-up.

- Connect the three BNC to E-Z clip cables (supplied with the CAT Box) to the SIGNATURE ANALYSIS CONTROL START, STOP and CLOCK jacks on the CAT Box.

- 3. Attach the three black E-Z clips to a ground loop on the Tempest™ game PCB.

- Attach the CAT Box data probe to the DATA jack on the CAT Box.

- 5. The colored E-Z clips on the cables will be moved about for each group of signatures to be taken.

The set-up for each group of signatures is located on the schematic sheet near the device to be checked. The signatures are located on or near the signal point on the schematic.

- 6. Set the CAT Box switches as follows:

- TESTER MODE: SIG

- TESTER SELF-TEST: OFF

- PULSE MODE: LATCHED

- START: As indicated

- STOP: As indicated

- CLOCK: As indicated

- 7. Power up the game board and the CAT Box.

## **B. Clock and Reset** Circuitry

**NOTE:** For this test, remove W DOG DIS from GROUND.

### 1. CAT Box Settings

| Probe | Trigger | IC-Pin |

|-------|---------|--------|

| Start |         | A6-6   |

| Stop  |         | D3-8   |

| Clock | ~~      | D3-8   |

#### 2. Signatures

| •                        |                |                        |

|--------------------------|----------------|------------------------|

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signature<br>Should Be |

| C4-3                     | 6MHz           | 1730                   |

| C4-2                     | 3MHz           | 3441                   |

| C4-6<br>C4-7             | 1.5MHz         | 5CPA<br>36H3           |

| F3-6                     | E3MHz          | 3441                   |

| F3-3<br>B4-8             | E6MHz          | 1730<br>7CUP           |

| B4-6                     | 3KHz           | P74P                   |

| D4-8<br>D4-6             |                | 3214<br>C4P5           |

| D3-8<br>E4-15            | RESET          | 4668<br>F0F1           |

| E3-12                    | _              | V990                   |

|                          |                |                        |

## C. Address Lines

# 1. CAT Box Settings for Address Bus Test

| Probe | Trigger | IC-Pin | Test Pt. |

|-------|---------|--------|----------|

| Start | 7_      | C2-25  |          |

| Stop  | _       | C2-25  |          |

| Clock | ī       | C2-39  | Φ2       |

### 2. Signatures

| Logic Probe  | Signal     | Signature    |

|--------------|------------|--------------|

| on IC-Pin    | Name       | Should Be    |

| B/C1-12      | AB0        | UUUU         |

| B/C1-14      | AB1        | 5555         |

| B/C1-16      | AB2        | CCCC         |

| B/C1-18      | AB3        | 7F7F         |

| B/C1-9       | AB4        | 5H21         |

| B/C1-7       | AB5        | 0AFA         |

| B/C1-5       | AB6        | UPFH         |

| B/C1-3       | AB7        | 52F8         |

| A/B1-12      | AB8        | HC89         |

| A/B1-14      | AB9        | 2H70         |

| A/B1-16      | AB10       | HPP0         |

| A/B1-18      | AB11       | 1293         |

| A/B1-3       | AB12       | HAP7         |

| B3-2         | A13        | 3C96         |

| B3-3<br>B3-1 | A14<br>A15 | 3827<br>755U |

| A6-4         | A15        | 755P         |

|              |            |              |

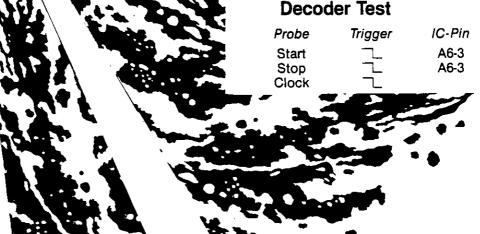

## D. Address Decoder

# 1. CAT Box Settings for Address Decoder Test

Test Pt.

Ф2

### 2. Signatures

NOTE: To obtain Signatures from IC J5, ground  $R/\overline{W}$  testpoint.

| Logic Probe | Signal          | Signature |

|-------------|-----------------|-----------|

| оп IC-Pin   | Name            | Should Be |

| B3-7        | Ī/Ō             | F2A6      |

| E3-2        | <u>i70</u>      | F2A7      |

| F3-8        | EI/O            | F2A6      |

| J5-9        | VGRST           | 5969      |

| J5-10       | WDCLR           | 0PC5      |

| J5-11       | <del>VGGO</del> | 270P      |

| J5-12       | BB*             | 9CH2      |

| B3-5        | VMEM            | 12U3      |

| B3-4        | AA*             | 4P0A      |

| J2-7        | ROM8            | 56C3      |

| J2-6        | ROM7            | 8019      |

| J2-5        | ROM6            | 5AH1      |

| J2-4        | ROM5            | 9HUC      |

| J2-9        | ROM4            | 1920      |

| J2-10       | ROM3            | C34C      |

| J2-11       | ROM2            | 597C      |

| J2-12       | ROM1            | UA87      |

| C1-7        | ROM0            | 4154      |

| C1-6        | ROMX            | 960F      |

|             |                 |           |

### 2. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| D1-9        | DB0    | 1F4H      |

| D1-10       | DB1    | 4P55      |

| D1-11       | DB2    | P2C5      |

| D1-13       | DB3    | UH32      |

| D1-14       | DB4    | 4HFA      |

| D1-15       | DB5    | 0P76      |

| D1-16       | DB6    | 86CP      |

| D1-17       | DB7    | P29C      |

# 3. CAT Box Settings for ROM0 Test (I.C. E1)

| Probe | Trigger  | Testpoint |

|-------|----------|-----------|

| Start | 7_       | ROM0      |

| Stop  | <u>_</u> | ROMO      |

| Clock | 7        | ф2        |

#### 4. Signatures

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signature<br>Should Be |

|--------------------------|----------------|------------------------|

| E1-9                     | DB0            | 6481                   |

| E1-10                    | DB1            | P6A9                   |

| E1-11                    | DB2            | 9552<br>4053           |

| E1-13                    | DB3            | 40F3                   |

| E1-14                    | DB4            | 37C2                   |

| E1-15                    | DB5            | 0A18                   |

| E1-16                    | DB6            | A2C0                   |

| E1-17                    | DB7            | 9HC5                   |

## E. ROM and Data Lines

NOTE: When taking signatures on ROMs, install a 270 pF capacitor between IC-Pin C2-23 and ground. This can be done in the socket at C2.

# 1. CAT Box Settings for ROMX Test (I.C. D1)

| Probe | Trigger | Testpoint |

|-------|---------|-----------|

| Start |         | ROMX      |

| Stop  | Ţ       | ROMX      |

| Clock | 7_      | ф2        |

# 5. CAT Box Settings for ROM1 Test (I.C. F1)

| Probe         | Trigger | Testpoint    |

|---------------|---------|--------------|

| Start         |         | ROM1<br>ROM1 |

| Stop<br>Clock | =       | ф2           |

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signature<br>Should Be |

|--------------------------|----------------|------------------------|

| F1-9                     | DB0            | 3892                   |

| F1-10                    | DB1            | 01U5                   |

| F1-11                    | DB2            | PH6P                   |

| F1-13                    | DB3            | UP9F                   |

| F1-14                    | DB4            | UP44                   |

| F1-15                    | DB5            | CA33                   |

| F1-16                    | DB6            | 3U05                   |

| F1-17                    | DB7            | 8CP3                   |

# 7. CAT Box Settings for ROM2 Test

| Trigger | Testpoint<br>ROM2<br>ROM2 |

|---------|---------------------------|

| ~       | Φ2                        |

|         | Trigger                   |

## 8. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| H1-9        | DB0    | T550      |

| H1-10       | DB1    | A01F      |

| H1-11       | DB2    | A540      |

| H1-13       | DB3    | 5U60      |

| H1-14       | DB4    | 2068      |

| H1-15       | DB5    | 9767      |

| H1-16       | DB6    | 54CA      |

| H1-17       | DB7    | 7F8F      |

# 9. CAT Box Settings for ROM3 Test

| Probe Start Stop | Trigger | Testpoint<br>ROM3 |

|------------------|---------|-------------------|

| Clock            | 7       | ROM3              |

# 10. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| J1-9        | DB0    | 09A6      |

| J1-10       | DB1    | 6A12      |

| J1-11       | DB2    | 91CA      |

| J1-13       | DB3    | 10HP      |

| J1-14       | DB4    | F53U      |

| J1-15       | DB5    | C67C      |

| J1-16       | DB6    | 8272      |

| J1-17       | DB7    | F651      |

# 11. CAT Box Settings for ROM4 Test (I.C. K1)

| Probe                  | Tri     |                           |

|------------------------|---------|---------------------------|

| Start<br>Stop<br>Clock | Trigger | Testpoint<br>ROM4<br>ROM4 |

|                        |         | Ф2                        |

# 12. Signatures

| 3a.n. 62    | 5      |           |

|-------------|--------|-----------|

| Logic Probe | Signal | Signature |

| on IC-Pin   | Name   | Should Be |

| K1-9        | DB0    | A8FU      |

| K1-10       | DB1    | U3U7      |

| K1-11       | DB2    | C8CH      |

| K1-13       | DB3    | 353F      |

| K1-14       | DB4    | 93FU      |

| K1-15       | DB5    | UFH1      |

| K1-16       | DB6    | A165      |

| K1-17       | DB7    | 5399      |

# 13. CAT Box Settings for ROM5 Test (I.C. L/M 1)

| Probe<br>Start<br>Stop<br>Clock | Trigger | Testpoint<br>ROM5<br>ROM5 |

|---------------------------------|---------|---------------------------|

|                                 | L       | Ф2                        |

# 14. Signatures

| 0           | 3      |           |

|-------------|--------|-----------|

| Logic Probe | Signal | Signature |

| on IC-Pin   | Name   | Should Be |

| UM1-9       | DB0    | 4876      |

| UM1-10      | DB1    | 5397      |

| UM1-11      | DB2    | 7396      |

| UM1-13      | DB3    | C9CH      |

| UM1-14      | DB4    | HF73      |

| UM1-15      | DB5    | 11U6      |

| UM1-16      | DB6    | 43C8      |

| UM1-17      | DB7    | 2P85      |

# 15. CAT Box Settings for ROM6 Test (I.C. M/N 1)

| Probe<br>Start<br>Stop<br>Clock | Trigger | Testpoint<br>ROM6<br>ROM6<br>#2 |

|---------------------------------|---------|---------------------------------|

|                                 | <u></u> | Φ2                              |

| Logic Probe on IC-Pin         Signal Name           M/N-9         DB0           M/N-10         DB1           M/N-11         DB2           M/N-13         DB3           M/N-14         DB4           M/N-15         DB5           M/N-16         DB6           M/N-17         DB7 | Signature<br>Should Be<br>A4AC<br>3A7C<br>0F22<br>H221<br>2H07<br>818A<br>1699 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| D87                                                                                                                                                                                                                                                                              | 4149                                                                           |

| 7. | CAT   | Box | <b>Settings</b> | for | ROM2 | Test |

|----|-------|-----|-----------------|-----|------|------|

|    | (I.C. | H1) | •               |     |      |      |

| Probe         | Trigger      | Testpoint    |

|---------------|--------------|--------------|

| Start<br>Stop | 7_           | ROM2<br>ROM2 |

| Clock         | <del>-</del> | φ2           |

## 8. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| H1-9        | DB0    | T550      |

| H1-10       | DB1    | A01F      |

| H1-11       | DB2    | A540      |

| H1-13       | DB3    | 5U60      |

| H1-14       | DB4    | 2068      |

| H1-15       | DB5    | 9767      |

| H1-16       | DB6    | 54CA      |

| H1-17       | DB7    | 7F8F      |

# 9. CAT Box Settings for ROM3 Test (I.C. J1)

| Probe         | Trigger | Testpoint    |

|---------------|---------|--------------|

| Start<br>Stop | }       | ROM3<br>ROM3 |

| Clock         |         | ф2           |

## 10. Signatures

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signature<br>Should Be |

|--------------------------|----------------|------------------------|

| ON IC-PIN                | IVAIIIC        | Should De              |

| J1-9                     | DB0            | 09A6                   |

| J1-10                    | DB1            | 6A12                   |

| J1-11                    | DB2            | 91CA                   |

| J1-13                    | DB3            | 10HP                   |

| J1-14                    | DB4            | F53U                   |

| J1-15                    | DB5            | C67C                   |

| J1-16                    | DB6            | 8272                   |

| J1-17                    | DB7            | F651                   |

|                          |                |                        |

# 11. CAT Box Settings for ROM4 Test (I.C. K1)

| Probe         | Trigger | Testpoint    |

|---------------|---------|--------------|

| Start<br>Stop | 7_      | ROM4<br>ROM4 |

| Clock         | £       | Ф2           |

## 12. Signatures

| Logic Probe | Signal     | Signature |

|-------------|------------|-----------|

| on IC-Pin   | Name       | Should Be |

| K1-9        | DB0        | A8FU      |

| K1-10       | DB1        | U3U7      |

| K1-11       | <b>DB2</b> | C8CH      |

| K1-13       | DB3        | 353F      |

| K1-14       | DB4        | 93FU      |

| K1-15       | DB5        | UFH1      |

| K1-16       | DB6        | A165      |

| K1-17       | DB7        | 5399      |

# 13. CAT Box Settings for ROM5 Test (I.C. L/M 1)

| Probe                  | Trigger | Testpoint          |

|------------------------|---------|--------------------|

| Start<br>Stop<br>Clock | 7-      | ROM5<br>ROM5<br>Ф2 |

## 14. Signatures

| Logic Probe | Sign <b>al</b> | Signature |

|-------------|----------------|-----------|

| on IC-Pin   | Name           | Should Be |

| L/M1-9      | DB0            | 4876      |

| L/M1-10     | DB1            | 5397      |

| L/M1-11     | DB2            | 7396      |

| L/M1-13     | DB3            | C9CH      |

| L/M1-14     | D84            | HF73      |

| L/M1-15     | D85            | 11U6      |

| L/M1-16     | D86            | 43C8      |

| L/M1-17     | D87            | 2P85      |

# 15. CAT Box Settings for ROM6 Test (I.C. M/N 1)

| Probe         | Trigger | Testpoint |

|---------------|---------|-----------|

| Start<br>Stop | 7_      | ROM6      |

| Clock         | 4       | Ф2        |

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signature<br>Should Be |

|--------------------------|----------------|------------------------|

| M/N-9                    | DB0            | A4AC                   |

| M/N-10                   | DB1            | 3A7C                   |

| M/N-11                   | DB2            | 0F22                   |

| M/N-13                   | DB3            | H221                   |

| M/N-14                   | DB4            | 2H07                   |

| M/N-15                   | DB5            | 818A                   |

| M/N-16                   | DB6            | 1699                   |

| M/N-17                   | DB7            | 4149                   |

# 17. CAT Box Settings for ROM7 Test (I.C. P1)

| Probe | Trigger | Testpoint |

|-------|---------|-----------|

| Start | ٦_      | ROM7      |

| Stop  |         | ROM7      |

| Clock | 7_      | Ф2        |

#### 18. Signatures

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signature<br>Should Be |

|--------------------------|----------------|------------------------|

| P1-9                     | DB0            | P4F3                   |

| P1-10                    | DB1            | 2C06                   |

| P1-11                    | DB2            | 4614                   |

| P1-13                    | DB3            | 7 <b>A6</b> 3          |

| P1-14                    | DB4            | 434C                   |

| P1-15                    | DB5            | 3C66                   |

| P1-16                    | DB6            | P8UC                   |

| P1-17                    | DB7            | 2C3A                   |

|                          |                |                        |

# 19. CAT Box Settings for ROM8 Test (I.C. R1)

| Probe | Trigger | Testpoint |

|-------|---------|-----------|

| Start |         | ROM8      |

| Stop  | =       | ROM8      |

| Clock |         | Ф2        |

### 20. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| R1-9        | DB0    | 9HFP      |

| R1-10       | DB1    | U7HH      |

| R1-11       | DB2    | F32H      |

| R1-13       | DB3    | F66U      |

| R1-14       | DB4    | U379      |

| R1-15       | DB5    | 490P      |

| R1-16       | DB6    | 5P99      |

| R1-17       | DB7    | CFA8      |

### 22. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| N/P3-9      | DB0    | H1U9      |

| N/P3-10     | DB1    | 5U8C      |

| N/P3-11     | DB2    | 0C59      |

| N/P3-13     | DB3    | 507P      |

| N/P3-14     | DB4    | 2A8P      |

| N/P3-15     | DB5    | 9F0C      |

| N/P3-16     | DB6    | AH97      |

| N/P3-17     | DB7    | 29AH      |

NOTE: When taking signatures on I.C. R3, ground IC-Pin B3-5.

# 23. CAT Box Settings for Vector ROM1 Test (I.C. R3)

| Probe | Trigger | IC-Pin | Testpoint |

|-------|---------|--------|-----------|

| Start | ~_      | R3-20  |           |

| Stop  |         | R3-20  |           |

| Clock |         |        | Ф2        |

### 24. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| R3-9        | DB0    | 3FH3      |

| R3-10       | DB1    | 0H59      |

| R3-11       | DB2    | 9H5H      |

| R3-13       | DB3    | 98PF      |

| R3-14       | DB4    | PA27      |

| R3-15       | DB5    | 5U3H      |

| R3-16       | DB6    | 97FC      |

| R3-17       | DB7    | 583A      |

NOTE: When taking signatures on IC N/P3, ground IC-Pin B3-5.

# 21. CAT Box Settings for Vector ROM Test (I.C. N/P3)

| Probe         | Trigger | IC-Pin             | Testpoint |

|---------------|---------|--------------------|-----------|

| Start<br>Stop | }       | N/P3-20<br>N/P3-20 |           |

| Clock         | Ę       | 1111 0 200         | Ф2        |

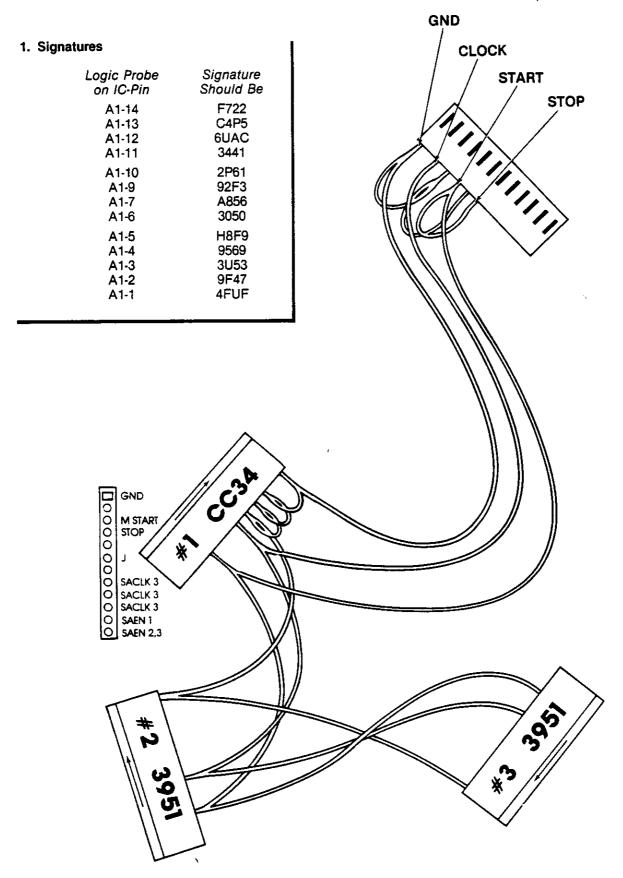

## F. Math Box

The Math Box signature analysis procedure is somewhat different from other procedures, so follow these set-up instructions for the three tests carefully.

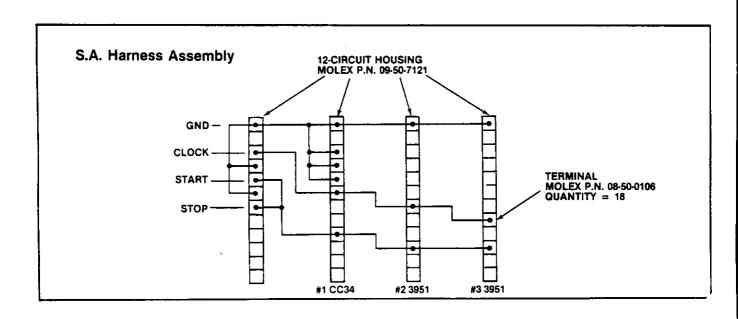

In addition to your CAT Box or signature analyzer, you'll need an SA Harness Assembly. Order Atari part number A036836-01 or see Figure 6 to make your own.

#### A. Math Box Test #1 Procedure:

- Plug SA Harness Assembly Test #1 connector onto Signature Analyzer connector (J16) on the Auxiliary PCB.

- Connect the CAT Box Start, Stop and Clock E-Z hooks to the SA Harness Assembly as shown in Figure 7.

- On the main PCB, connect PWR ON RESET test point to ground, and power-up the game and the CAT Box.

- Don't remove the microprocessor (6502A) from the main PCB.

Don't connect the 50 pin ribbon cable to the main PCB edge connector.

Don't connect W DOG DIS to ground.

- 5. Set the CAT Box switches as follows:

- a. START \_\_\_ b. STOP \_\_\_

- c. CLOCK\_\_

- d. TESTER MODE: SIG

- e. Press TESTER RESET

- With the logic probe touching the +5V test point on the Auxiliary PCB, the ADDRESS/SIGNATURE display should read CC34. This will verify that your test set-up is correct. If you don't get CC34, recheck your set-up.

NOTE: Signatures are listed in the order that they should be done. As often as possible, IC-Pin refers to a chip output. As a general rule, when a bad signature is discovered, the IC listed in the IC-Pin column can be suspected as faulty.

Those signatures marked with an asterisk (\*) should be taken with a 1K resistor clipped between the logic probe and the +5V test point.

| 1. | Signatures |

|----|------------|

|----|------------|

| ires                     |                        |

|--------------------------|------------------------|

| Logic Probe<br>on IC-Pin | Signature<br>Should Be |

| C1-11                    | H58A                   |

| C1-12                    | 77F7                   |

| C1-13<br>C1-14           | 85PA<br>7P25           |

| D1-11                    | 5CP0                   |

| D1-12                    | P5PH                   |

| D1-13<br>D1-14           | 725C<br>96PF           |

| F1-12                    | 4PPF                   |

| F1-11                    | OUF0                   |

| F1-10<br>F1-9            | 3CAP<br>A6A3           |

| H1-12                    | 26A6                   |

| H1-11                    | 91HA<br>P9C1           |

| H1-10<br>H1-9            | 2987                   |

| J1-12                    | 96U0                   |

| J1-11<br>J1-10           | UC59<br>6989           |

| J1-10                    | 3FU4                   |

| K1-12                    | 05A6                   |

| K1-11<br>K1-10           | 60H6<br>PPF6           |

| K1-9                     | 34C2                   |

| L1-12                    | 58A1                   |

| L1-11<br>L1-10           | 1AA2<br>F74F           |

| L1-9                     | 6CF6                   |

| E1-12                    | F765                   |

| E1-11<br>E1-10           | CPU8<br>0000           |

| E1-10                    | F515                   |

| F4-2                     | CC34                   |

| E4-6                     | A6A3                   |

| A2-6<br>B1-2             | 0000<br>8A7H           |

| B1-5                     | CU2P                   |

| B1-6                     | 1C6C                   |

| B1-9<br>B1-12            | 6U30<br>5AAH           |

| B1-15                    | 03A7                   |

| B1-16                    | 9A08                   |

| B1-19<br>K/L2-33         | 2327<br>6PUP           |

|                          |                        |

| K/L2-16<br>K/L2-8        | 9AFH*<br>809A*         |

| F/H2-33                  | 9CPP                   |

| F/H2-16                  | 11C5*                  |

| F/H2-8 | 78AA* |

|--------|-------|

| J2-33  | 8638  |

| J2-16  | 11C5* |

| J2-8   | 7U19* |

| E2-34  | A1F7  |

| E2-31  | 1781  |

| E2-16  | 9AFH* |

| E5-11  | C646  |

| D4-8   | 0600  |

| E4-11  | CC34  |

| F5-11  | C835* |

| D4-6   | C4U4  |

| F5-6   | 753F  |

| E4-8   | CPU8  |

| E5-8   | 45A1* |

#### B. Math Box Test #2A Procedure

- Plug SA Harness Assembly Test #2 connector onto Signature Analyzer connector (J16) on the Auxiliary PCB.

- Connect the CAT Box Start, Stop and Clock E-Z hooks to the SA Harness Assembly as shown in Figure 7.

- 3. Don't remove the microprocessor (6502A) from the main PCB.

Don't connect the 50 pin ribbon cable to the main PCB edge connector.

Don't connect W DOG DIS to ground.

Don't connect PWR ON RESET to ground.

- 4. Set the CAT Box switches as follows:

- a. START

- b. STOP \_\_\_

- c. CLOCK \_\_

- d. TESTER MODE: SIG

- e. Press TESTER RESET

- Enter the self-test mode and advance the screen with the slam switch until the large rectangle appears. This procedure is described in Figure 6, Chapter 2 of the Tempest™ Operation, Maintenance, and Service Manual.

- With the logic probe touching the +5V test point on the Auxiliary PCB, the ADDRESS/SIGNATURE display should read 3951. This will verify that your test set-up is correct. If you don't get 3951, recheck your set-up.

NOTE: Signatures are listed in the order that they should be done. As often as possible, *IC-Pin* refers to a chip output. As a general rule, when a bad signature is discovered, the IC listed in the *IC-Pin* column can be suspected as faulty.

Figure 7 S.A. Harness Assembly

#### B. Math Box Test #2B **Procedure**

- 1. Plug SA Harness Assembly Test #2 connector onto Signature Analyzer connector (J16) on the Auxiliary PCB.

- 2. Connect the CAT Box Start, Stop and Clock E-Z hooks to the SA Harness Assembly as shown in Figure 7.

- 3. Don't remove the microprocessor (6502A) from the main PCB.

Don't connect the 50 pin ribbon cable to the main PCB edge connector.

Don't connect W DOG DIS to ground.

Don't connect PWR ON RESET to ground.

- 4. Set the CAT Box switches as follows:

- a. START \_\_

- b. STOP

- c. CLOCK \_

- d. TESTER MODE: SIG

- e. Press TESTER RESET

- 5. Enter the self-test mode and advance the screen with the slam switch until the large rectangle appears. This procedure is described in Figure 6, Chapter 2 of the Tempest<sup>™</sup> Operation, Maintenance, and Service Manual.

- 6. With the logic probe touching the +5V test point on the Auxiliary PCB, the ADDRESS/SIGNATURE display should read 3951. This will verify that your test set-up is correct. If you don't get 3951, recheck your set-up.

NOTE: Signatures are listed in the order that they should be done. As often as possible, IC-Pin refers to a chip output. As a general rule, when a bad signature is discovered, the IC listed in the IC-Pin column can be suspected as faulty.

#### 1. Signatures

| Logic Probe<br>on IC-Pin | Signature<br>Should Be |

|--------------------------|------------------------|

| C1-11                    | 92F3                   |

| C1-12                    | A856                   |

| C1-13                    | 3050                   |

| C1-14                    | H8F9                   |

| D1-11                    | 9569                   |

| D1-12                    | 3U53                   |

| D1-13                    | 9F47                   |

| D1-14                    | 4FUF                   |

#### B. Math Box Test #3 Procedure

- 1. Plug SA Harness Assembly Test #3 connector onto Signature Analyzer connector (J16) on the Auxiliary PCB.

- 2. Connect the CAT Box Start, Stop and Clock E-Z hooks to the SA Harness Assembly as shown in Figure 7.

- 3. Don't remove the microprocessor (6502A) from the main PCB.

Don't connect the 50 pin ribbon cable to the main PCB edge connector.

Don't connect W DOG DIS to ground. Don't connect PWR ON RESET to ground.

- 4. Set the CAT Box switches as follows:

- a. START

- b. STOP

- c. CLOCK

- d. TESTER MODE: SIG

- e. Press TESTER RESET

- 5. Enter the self-test mode and advance the screen with the slam switch until the large rectangle appears. This procedure is described in Figure 6, Chapter 2 of the Tempest™ Operation, Maintenance, and Service Manual.

- 6. With the logic probe touching the +5V test point on the Auxiliary PCB, the ADDRESS/SIGNATURE display should read 3951. This will verify that your test set-up is correct. If you don't get 3951, recheck your set-up.

NOTE: Signatures are listed in the order that they should be done. As often as possible, IC-Pin refers to a chip output. As a general rule, when a bad signature is discovered, the IC listed in the IC-Pin column can be suspected as faulty.

| Logic Probe<br>on IC-Pin | Signature<br>Should Be |

|--------------------------|------------------------|

| E2-22                    | 1441                   |

| E2-23                    | 2883                   |

| E2-24                    | 5107                   |

| E2-25                    | A20P                   |

| J2-22                    | 441H                   |

| J2-23                    | 883A                   |

| J2-24                    | 1074                   |

| J2-25                    | 20P9                   |