# **Signetics**

## 68000 16-/32-Bit Microprocessor

Product Specification

#### Military Customer Specific Products

#### DESCRIPTION

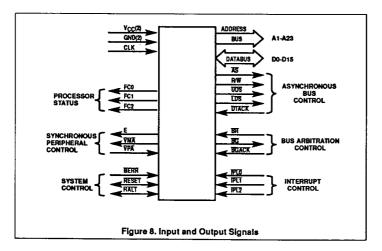

The 68000 is the first implementation of the 68000 16/32 bit microprocessor architecture. The 68000 has a 16-bit data bus and 24-bit address bus, while the full architecture provides for 32-bit address and data buses. It is completely code-compatible with the 68008 8-bit data bus implementation of the 68000 and is downward code-compatible with the 68010 virtual extension and the 68020 32-bit implementation of the architecture. Any user-mode programs written using the 68000 instruction set will run unchanged on the 68008, 68010, and 68020. This is possible because the user programming model is identical for all four processors and the instruction sets are proper sub-sets of the complete architecture.

The 68000 possesses an asynchronous bus structure with a 24-bit address bus and a 16-bit data bus.

The resources available to the 68000 user consist of the following:

- 17 32-bit data and address registers

- 16MB direct adressing registers

- 56 powerful instruction types

- Operations on five main data types

- Memory-mapped I/O

- 14 addressing modes

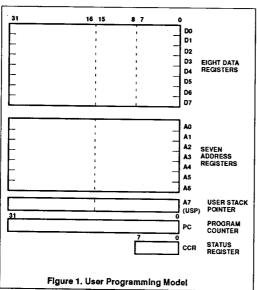

As shown in the programming model (Figure 1), the 68000 offers sixteen 32-bit registers and a 32-bit program counter. The first eight registers (D0 - D7) are used as data registers for byte (8-bit), word (16-bit), and long-word (32-bit) operations. The second set of seven registers (A0 - A6) and the user stack pointer (USP) may be used as software stack pointers and base address registers. In addition, the registers may be used for word and long-word operations. All of the 16 registers may be used as index registers.

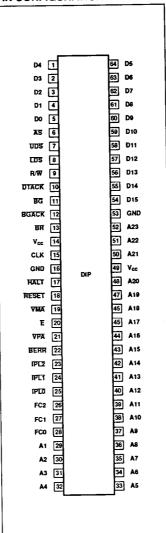

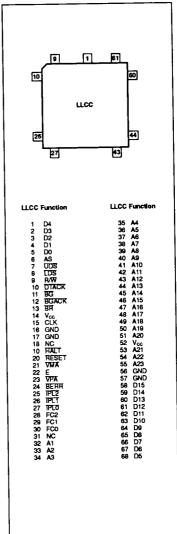

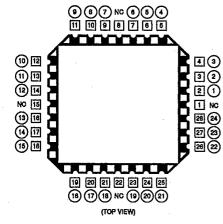

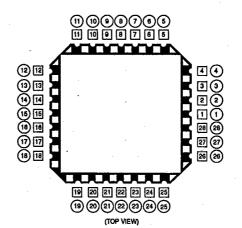

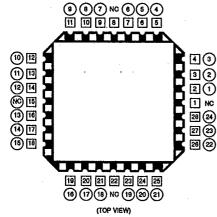

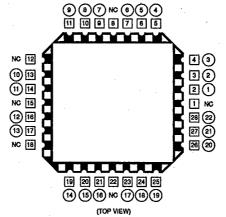

#### PIN CONFIGURATION

#### PIN CONFIGURATION

68000

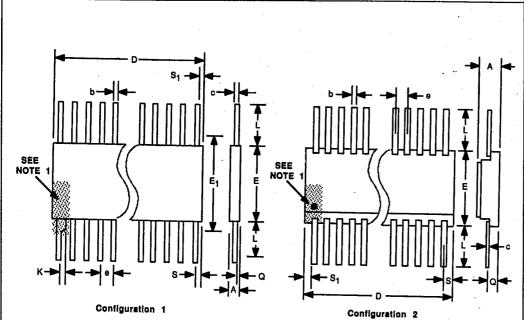

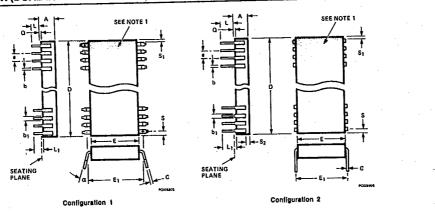

#### **ORDERING INFORMATION**

| DESCRIPTION                    | ORDER CODE   | SPEED |

|--------------------------------|--------------|-------|

|                                | 68000-6/BXA  | 6MHz  |

| 64-Pin Ceramic DIP 900mil-wide | 68000-8/BXA  | 8MHz  |

|                                | 68000-10/BXA | 10MHz |

|                                | 68000-6/BUC  | 6MHz  |

| 68-Pin Ceramic LLCC            | 68000-8/BUC  | 8MHz  |

|                                | 68000-10/BUC | 10MHz |

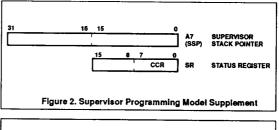

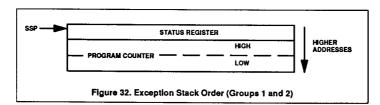

In supervisor mode, the upper byte of the status register and the supervisor stack pointer (SSP) are also available to the programmer. These registers are shown in Figure 2.

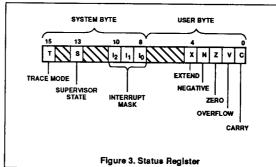

The status register, Figure 3, contains the interrupt mask (eight levels available) as well as the condition codes: extend (X), negative (N), zero (Z), overflow (V), and carry (C). Additional status bits indicate that the processor is in a trace (T) mode and in a supervisor (S) or user state.

**Table 1. Addressing Modes**

| ADDRESSING MODES                                                                                                                                                                  | SYNTAX                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Register direct addressing<br>Data register direct<br>Address register direct                                                                                                     | Dn<br>An                                                                   |

| Absolute data addressing<br>Absolute short<br>Absolute long                                                                                                                       | xxx.W<br>xxx.L                                                             |

| Program counter relative addressing<br>Relative with offset<br>Relative with index and offset                                                                                     | d <sub>16</sub> (PC)<br>d <sub>8</sub> (PC,Xn)                             |

| Register Indirect addressing Register indirect Postincrement register indirect Predecrement register indirect Register indirect with offset Indexed register indirect with offset | (An)<br>(An) +<br>- (An)<br>d <sub>16</sub> (An)<br>d <sub>8</sub> (An,Xn) |

| Immediate data addressing Immediate Quick immediate                                                                                                                               | #xxx<br>#1 - #8                                                            |

| Implied addressing Implied register                                                                                                                                               | SR/USP/SP/PC                                                               |

#### NOTES:

On = Data register

An = Address register

Xn = Address or data register used as index

register

SR = Status register

PC = Program counter

SP = Stack pointer

USP = User stack pointer

() = Effective Address

d<sub>8</sub> = 8-bit offset (displacement)

d<sub>16</sub> = 16-bit offset (displacement)

#xxx = Immediate data

#### **Data Types and Addressing** Modes

Five basic data types are supported. These data types are:

- BCD digits (4 bits)

- Bytes (8 bits)

- Words (16 bits)

- Long words (32 bits)

In addition, operations on other data types such as memory addresses, status word data, etc., are provided in the instruction set.

The 14 address modes, shown in Table 1, include six basic types:

- Register direct

- Register indirect

- Absolute

- Program counter relative

- Immediate

- implied

Included in the register indirect addressing modes is the capability to do preincrementing, predecrementing, offsetting, and indexing. The program counter relative mode can also be modified via indexing and offsetting.

68000

**Table 2. Instruction Set Summary**

| Table 2. Instruction 9  | Set Summary                          |

|-------------------------|--------------------------------------|

| MNEMONIC                | DESCRIPTION                          |

| ABCD                    | Add decimal with extend              |

| ADD                     | Add                                  |

| AND                     | Logical AND                          |

| ASL                     | Arithmetic shift left                |

| ASR                     | Arithmetic shift right               |

| B <sub>CC</sub><br>BCHG | Branch conditionally                 |

| BCHG                    | Bit test and change                  |

| BRA                     | Bit test and clear<br>Branch always  |

| BSET                    | Bit test and set                     |

| BSR                     | Branch to subroutine                 |

| BTST                    | Bit test                             |

| СНК                     | Check register against bounds        |

| CLR                     | Clear operand                        |

| СМР                     | Compare                              |

| DB <sub>CC</sub>        | Test condition, decrement and branch |

| DIVS                    | Signed divide                        |

| DIVU                    | Unsigned divide                      |

| EOR                     | Exclusive OR                         |

| EXG                     | Exchange registers                   |

| EXT                     | Sign extend                          |

| JMP                     | Jump                                 |

| JSR                     | Jump to subroutine                   |

| LEA                     | Load effective address               |

| LINK                    | Link stack                           |

| LSL<br>LSR              | Logical shift left                   |

| MOVE                    | Logical shift right                  |

| MULS                    | Move source to destination           |

| MULU                    | Signed multiply Unsigned multiply    |

| NBCD                    | Negate decimal with extend           |

| NEG                     | Negate decimal with extend           |

| NOP                     | No operation                         |

| NOT                     | One's complement                     |

| OR                      | Logical OR                           |

| PEA                     | Push effective address               |

| RESET                   | Reset external devices               |

| ROL                     | Rotate left without extend           |

| ROR                     | Rotate right without extend          |

| ROXL                    | Rotate left with extend              |

| ROXR                    | Rotate right with extend             |

| RTE                     | Return from exception                |

| RTR                     | Return and restore                   |

| RTS                     | Return from subroutine               |

| SBCD                    | Subtract decimal with extend         |

| S <sub>CC</sub><br>STOP | Set conditional Stop                 |

| SUB                     | Subtract                             |

| SWAP                    | Swap data register halves            |

| TAS                     | Test and set operand                 |

| TRAP                    | Trap                                 |

| TRAPV                   | Trap on overflow                     |

| TST                     | Test                                 |

| UNLK                    | Unlink                               |

|                         | <u> </u>                             |

#### Instruction Set Overview

The 68000 instruction set is shown in Table 2. Some additional instructions are variations, or subsets of these, and they appear in Table 3. Special emphasis has been given to the instruction set's support of structured high-level languages to facilitate ease of programming. Each instruction, with few exceptions, operates on bytes, words, and long words and most instructions can use any of the 14 addressing modes. Combining instruction types, data types, and addressing modes, over 1000 useful instructions are provided. These instructions include signed and unsigned, multiply and divide, "quick" arithmetic operations, BCD arithmetic, and expanded operations (through traps).

Table 3. Variations of Instruction Types

| INSTRUCTION TYPE | VARIATION                                                      | DESCRIPTION                                                                                                                                                               |

|------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD              | ADD<br>ADDA<br>ADDQ<br>ADDI<br>ADDX                            | Add Add address Add quick Add immediate Add with extend                                                                                                                   |

| AND              | AND<br>ANDI<br>ANDI to CCR<br>ANDI to SR                       | Logical AND AND immediate AND immediate to condition codes AND immediate to register status                                                                               |

| СМР              | CMP<br>CMPA<br>CMPM<br>CMPI                                    | Compare Compare address Compare memory Compare immediate                                                                                                                  |

| EOR              | EOR<br>EORI<br>EORI to CCR<br>EORI to SR                       | Exclusive-OR Exclusive-OR immediate Exclusive-OR immediate to condition codes Exclusive-OR immediate to status register                                                   |

| MOVE             | MOVE MOVEA MOVEM MOVEP MOVEQ MOVE from SR MOVE to CCR MOVE USP | Move source to destination Move address Move multiple registers Move peripheral data Move quick Move from status register Move to condition codes Move user stack pointer |

| NEG              | NEG<br>NEGX                                                    | Negate<br>Negate with extend                                                                                                                                              |

| OR               | OR<br>ORI<br>ORI to CCR<br>ORI to SR                           | Logical OR OR immediate OR immediate to condition codes OR immediate to status register                                                                                   |

| SUB              | SUB<br>SUBA<br>SUBI<br>SUBQ<br>SUBX                            | Subtract Subtract address Subtract immediate Subtract quick Subtract with extend                                                                                          |

## DATA ORGANIZATION AND ADDRESSING CAPABILITIES

This section contains a description of the registers and the data organization of the 68000.

#### **Operand Size**

Operand sizes are defined as follows: a byte equals 8 bits, a word equals 16 bits, and a long word equals 32 bits. The operand size for each instruction is either explicitly encoded in the instruction or implicitly defined by the instruction operation. Implicit instructions support some subset of all three sizes.

#### **Data Organization in Registers**

The eight data registers support data operands of 1, 8, 16, or 32 bits. The seven address registers together with the stack pointers support address operands of 32 bits.

#### Data Registers

Each data register is 32 bits wide. Byte operands occupy the low-order 8 bits, word operands the low-order 16 bits, and long-word operands the entire 32 bits. The least significant bit is addressed as bit zero; the most significant bit is addressed as 31.

When a data register is used as either a source or destination operand, only the appropriate low-order portion is changed; the remaining high-order portion is neither used nor changed.

#### Address Registers

Each address register and the stack pointer is 32 bits wide and holds a full 32-bit address. Address registers do not support the sized operands. Therefore, when an address register is used as a source operand, either the low-order word or the entire long-word operand is used depending on the operation size. When an address register is used as the destination operand, the entire register is affected regardless of the operation size. If the operation size is word, any other operands are sign extended to 32 bits before the operation is performed.

#### **Data Organization in Memory**

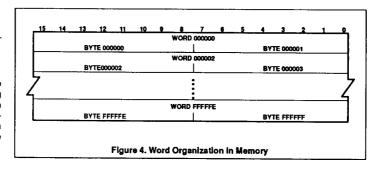

Bytes are individually addressable with the high-order byte having an even address the same as the word, as shown in Figure 4. The low-order byte has an odd address that is one count higher than the word address. Instructions and multibyte data are accessed only on word (even byte) boundaries. If a long-word datum is located at address n (n even), then the second word of that datum is located at address n + 2.

The data types supported by the 68000 are: bit data, integer data of 8, 16, or 32 bits, 32-bit addresses and binary-coded decimal data. Each of these data types is put in memory, as shown in Figure 5. The numbers indicate the order in which the data would be accessed from the processor.

#### Addressing

Instructions for the 68000 contain two kinds of information: the type of function to be performed and the location of the operand(s) on which to perform that function. The methods used to locate (address) the operand(s) are explained in the following paragraphs.

Instructions specify an operand location in one of three ways:

Register specification – the number of the register is given in the register field of their instruction.

Effective address – use of the different effective addressing modes.

Implicit reference - the definition of certain instructions implies the use of specific registers.

#### Instruction Format

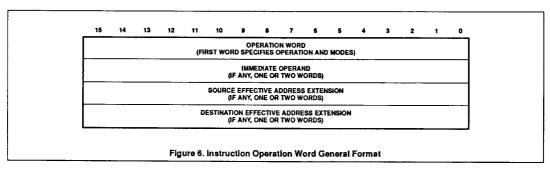

Instructions are from one to five words in length as shown in Figure 6. The length of the instruction and the operation to be performed is specified by the first word of the instruction which is called the operation word. The remaining words further specify the operands. These words are either immediate operands or extensions to the effective address mode specified in the operation word.

#### Program/Data References

The \$8000 separates memory references into two classes: program references and data references. Program references, as the name implies, are references to that section of memory that contains the program being executed. Data references refer to that section of memory that contains data. Operand reads are from the data space except in the case of the program counter relative addressing mode. All operand writes are to the data space.

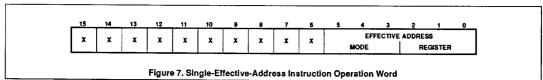

#### **Register Specification**

The register field within an instruction specifies the register to be used. Other fields within the instruction specify whether the register selected is an address or data register and how the register is to be used.

|           |        |                            |                      |    | 8 5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BYTE - 8                                                      | BITS<br>2      | 1        | 0      |            |         |   |          |

|-----------|--------|----------------------------|----------------------|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------|----------|--------|------------|---------|---|----------|

|           |        |                            |                      |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                |          |        |            |         |   |          |

| 15        | 14     | 13                         | 12                   | 11 | INTE<br>10 | EGER DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 - 1 BITE =                                                  | 8 BITS<br>6    | 5        | 4      | 3          | 2       | 1 | 0        |

| MSB       |        | ВУ                         | TE 0                 |    |            | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                               |                |          | BYTE 1 |            |         |   |          |

|           |        | ВҮ                         | TE 2                 |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                |          | BYTE 3 |            |         |   |          |

|           |        |                            | 40                   |    | 10         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D = 16 BITS                                                   | ;<br>6         | 5        | 4      | 3          | 2       | 1 | 0        |

| 15        | 14     | 13                         | 12                   | 11 | 10         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ORD 0                                                         |                |          |        | . <u> </u> |         |   | LSB      |

| MSB       |        |                            |                      |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ORD 1                                                         |                |          |        |            |         |   |          |

|           |        |                            |                      |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ORD 2                                                         |                |          |        |            |         |   |          |

|           |        |                            |                      |    |            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                               | NTO.           |          |        | -          |         |   |          |

| 15<br>MSB | 14     | 13                         | 12                   | 11 | 10         | 9 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ORD = 32 1<br>7<br>H ORDER                                    | 6              | 5        | 4      | 3          | 2       | 1 | 0        |

|           | L      | ONG WO                     | ORD 0                |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | — — — -                                                       |                |          |        |            |         |   |          |

|           |        |                            |                      |    |            | LO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ORDER                                                         |                |          |        |            |         |   | LSB      |

|           |        | ONG W                      | DD 1                 |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                |          |        |            |         |   |          |

|           |        |                            |                      |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                |          |        |            |         |   |          |

|           |        |                            |                      |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | *                                                             |                |          |        |            |         |   |          |

| <b></b>   | L      | ONG W                      | ORD 2                |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                |          |        |            |         |   |          |

|           |        |                            |                      |    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                |          |        |            |         |   |          |

| L         |        |                            |                      |    | ADD        | DECCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4 ADDDES                                                      | : _ 32 Bi      | ITS      |        |            |         |   |          |

| 15        | 14     | 13                         | 12                   | 11 | ADD<br>10  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 ADDRES:<br>8 7                                              | 6 = 32 Bi      | TS 5     | 4      | 3          | 2       | 1 | 0        |

| 15<br>MSB | 14     |                            |                      | 11 | ADD<br>10  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 ADDRESS<br>8 7<br>SH ORDER                                  | 3 = 32 Bi      | 5        | 4      | 3          | 2       | 1 | 0        |

|           | 14     | 13                         |                      | 11 | ADD<br>10  | 9<br>HIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8 7                                                           | 3 = 32 Bi<br>6 | 5        | 4      | 3          | 2       | 1 | 0<br>LSB |

|           | _      | ADDRE                      | SS 0                 | 11 | ADD:       | 9<br>HIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8 7<br>SH ORDER                                               | 3 = 32 Bi      | 5        | 4      | 3          | 2       | 1 |          |

|           | _      |                            | SS 0                 |    | ADD10      | 9<br>HIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8 7<br>SH ORDER                                               | 3 = 32 Bi      | 5<br>5   | 4      | 3          | 2       | 1 |          |

|           | _      | ADDRE                      | SS 0                 | 11 | ADD: 10    | 9<br>HIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8 7<br>SH ORDER                                               | 3 = 32 Bi      | 5        | 4      | 3          | 2       | 1 |          |

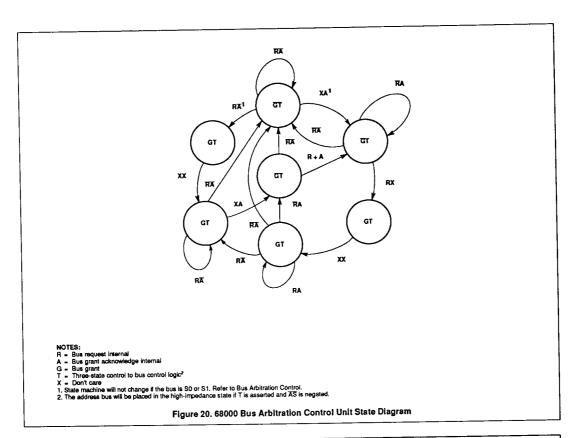

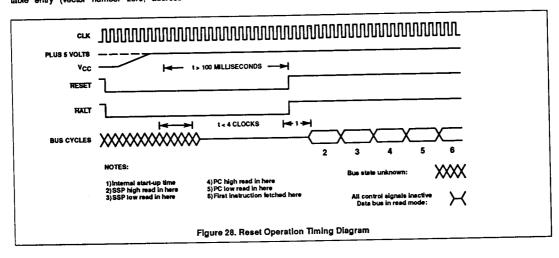

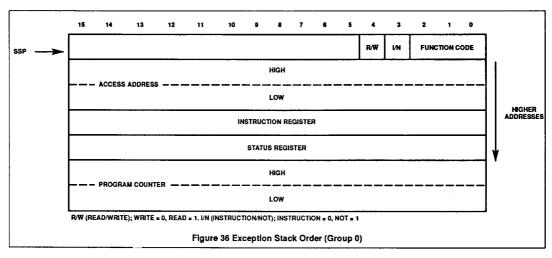

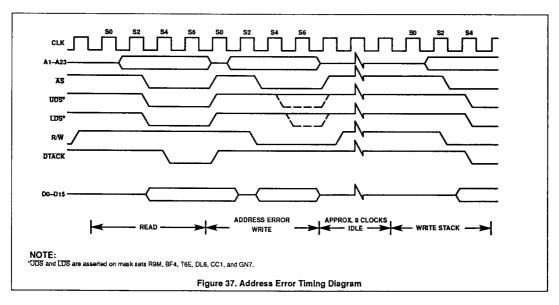

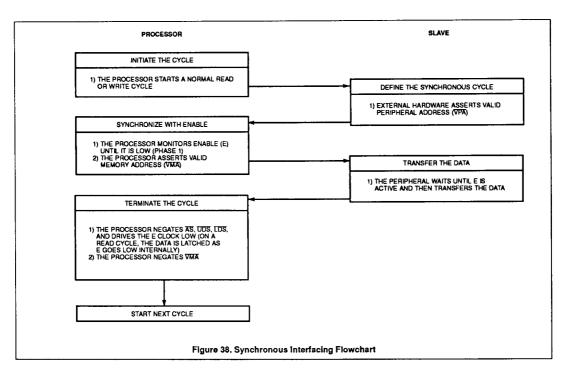

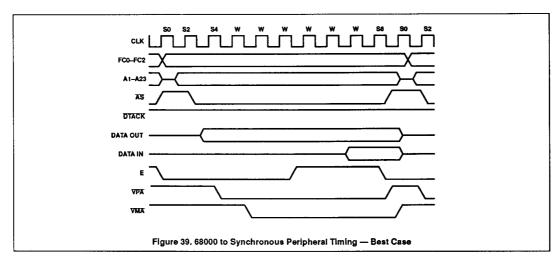

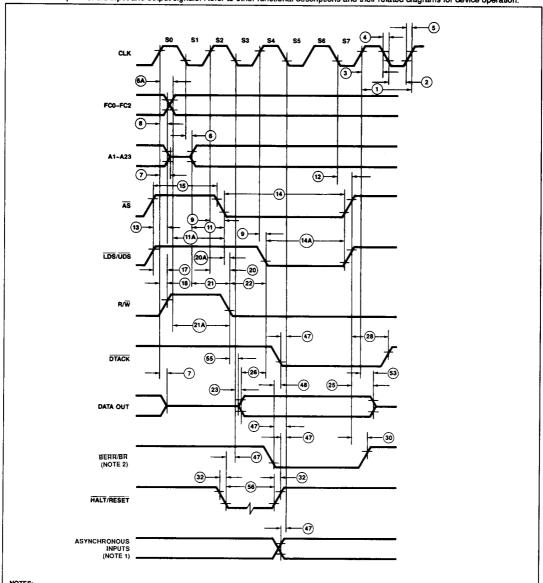

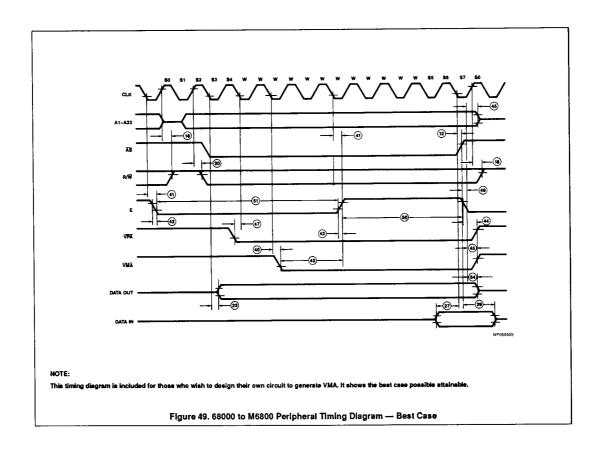

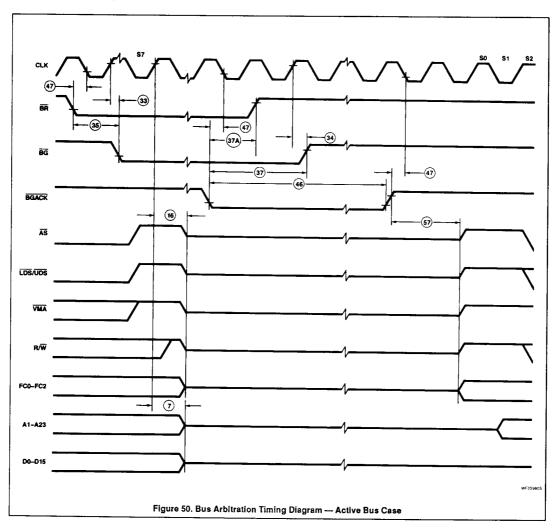

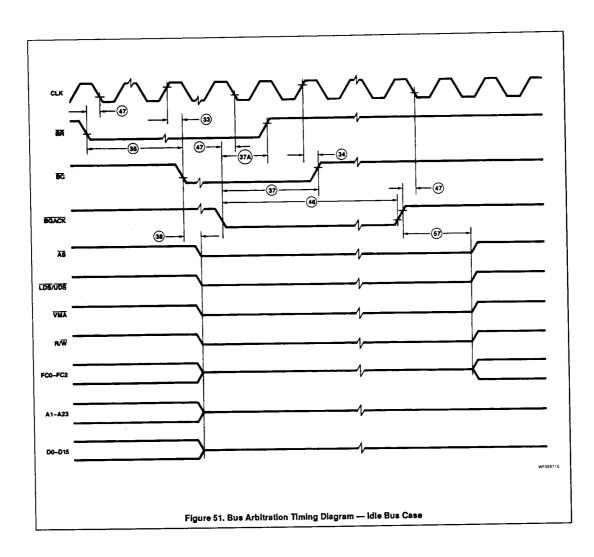

|           | _      | ADDRE                      | SS 0                 | 11 | ADD) 10    | 9<br>HIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8 7<br>SH ORDER                                               | 3 = 32 Bi      | 5        | 4      | 3          | 2       |   |          |