### TROUBLESHOOTING GUIDE

Complete with Signatures and Memory Map

### **Table of Contents**

| 1    | Memory Map                                                                                                                                                                                                                            | •                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 2    | Watchdog                                                                                                                                                                                                                              | 2                     |

| 3    | -Troubleshooting Using the CAT Box  A. CAT Box Preliminary Set-up  B. Address and Data Lines  C. RAM  D. Option Switch Inputs  E. Custom Audio I/O Chips  F. Player Input Switches and Encoder Wheel  G. LED and Coin Counter Outputs | 2 2 3 3 4 5           |

| 4    | Troubleshooting with Signature Analysis  A. Signature Analysis Set-up  B. Clock and Reset Circuitry  C. Address Lines  D. Address Decoder  E. ROM and Data Lines  F. Math Box                                                         | 6<br>7<br>7<br>7<br>8 |

|      |                                                                                                                                                                                                                                       | ,                     |

| lict | of Illustrations                                                                                                                                                                                                                      |                       |

### List of Illustrations

| Figure 2 | Memory Map                   | 3 |

|----------|------------------------------|---|

|          | Custom Audio I/O Chips       |   |

| •        | Analog Vector-Generator Data |   |

|          | S.A. Harness Assembly        |   |

## 1 Memory Map

| MEMORY MAP                                                  |                  |       |        |        |          |          |        |        |        |                                                                                                                                                          |

|-------------------------------------------------------------|------------------|-------|--------|--------|----------|----------|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| HEXA-<br>DECIMAL<br>ADDRESS                                 | R/W              | D7    | D6     | D5     | DA<br>D4 | TA<br>D3 | D2     | D1     | D0     | FUNCTION                                                                                                                                                 |

| . 0000-7FFF<br>0800-080F                                    | RW<br>W          | D     | D      | D      | D        | D<br>D   | D<br>D | D<br>D | D<br>D | Program RAM (2K)<br>Color RAM                                                                                                                            |

| 0C00<br>0C00<br>0C00<br>0C00<br>0C00<br>0C00<br>0C00<br>0C0 | ****             | D D D | D<br>D | D<br>D | D        | D<br>D   | D      | 0 0 0  | 00 0   | Right Coin Switch Center Coin Switch Left Coin Switch Slam Switch Self-Test Switch Diag. Step Switch HALT 3KHz Option Switch Inputs Option Switch Inputs |

| 2000-2FFF<br>3000-3FFF                                      | R/W<br>R         | D D   | D<br>D | D<br>D | D<br>D   | D D      | D<br>D | D      | D<br>D | Vector RAM (4K)<br>Vector ROM (4K)                                                                                                                       |

| 4000<br>4000<br>4000<br>4000<br>4800                        | W<br>W<br>W<br>W |       |        |        | D        | D        |        | D.     | ם      | Right Coin Counter<br>Center Coin Counter<br>Video Invert X<br>Video Invert Y<br>VG GO                                                                   |

| 5000<br>5800                                                | W                |       |        |        |          |          |        |        |        | WD CLEAR<br>VG Reset                                                                                                                                     |

| 6000-603F<br>6040<br>6040<br>6050                           | W<br>W<br>R      | 0000  | D<br>D | D D    | D<br>D   | D<br>D   | D D    | D<br>D | 0 00   | EAROM Write EAROM Control Math Box Status EAROM Read                                                                                                     |

| 6060<br>6070<br>6080-609F                                   | R<br>R<br>W      | 000   | 0 0 0  | DDD    | 000      | 0 0 0    | 0 0 0  | םםם    | םםם    | Math Box Read<br>Math Box Read<br>Math Box Start                                                                                                         |

| 60C0-60CF<br>60D0-60DF                                      | R/W<br>R/W       | ם ם   | D D    | D<br>D | D<br>D   | D<br>D   | D      | D<br>D | D<br>D | Custom Audio Chip 1<br>Custom Audio Chip 2                                                                                                               |

| 60E0<br>60E0<br>60E0                                        | R R R            |       |        |        |          |          | D      | D      | D      | One Player Start<br>Two Player Start<br>FLIP                                                                                                             |

| 9000-DFFF                                                   | R                | D     | D      | D      | D        | D        | D      | ۵      | D      | Program ROM (20K)                                                                                                                                        |

Figure 1 Memory Map

### 2 Watchdog

The Watchdog circuit will cause continuous reset pulses to the microprocessor if a problem exists within the microprocessor circuit. If the self-test falls to run, it is a good practice to check the reset line.

RESET-microprocessor input (pin 40). In a properly operating game, reset should occur during power-up or when the reset push button is activated. A pulsing reset line indicates that something is causing the microprocessor to lose its place within its program. Typical causes are:

- 1. Open or shorted address or data bus lines

- 2. Bad microprocessor chip

- 3. Bad bus buffers

- 4. Bad ROM

- 5. Bad RAM

- Any bad input or output that causes an address or data line to be held in a constant high or low state

A pulsing RESET signal indicates a problem exists somewhere within the microprocessor circuitry rather than within either the Math Box or the Analog Vector Generator.

## **Troubleshooting**

Using the CAT Box

### M. CAT Box Prelimimary Set-up

### IL Remove:

- O The electrical power from the game.

- O The wiring harnesses from the game PCBs.

- O the main and auxiliary boards from the game cabinet.

- The microprocessor chip C2 from the main PCB.

#### 2. Connect:

- The harnesses from the game to the main and auxiliary boards. (Use extender cables if available.)

- Ο Φ0 and φ2 test points together.

- O WD DIS test point to ground.

- The CAT Box flex cable to the main PCB test edge connector.

#### 3. Power Up:

- The game.

- The CAT Box.

#### 4. Set CAT Box Switches:

- TESTER SELF-TEST: (OFF)

- TESTER MODE: R/W

- Press TESTER RESET

### B. Address and Data Lines

NOTE: This section assumes that IC F2 is a 74LS245.

- 1. Perform the CAT Box preliminary set-up.

- Connect the DATA PROBE to the CAT Box and the game ground test point.

- 3. TESTER MODE: R/W

- 4. BYTES: 1.

- 5. PULSE MODE: UNLATCHED

- 6. R/W MODE: (OFF)

- 7. Key in address pattern on the keyboard (use AAAA to start)

- 8. Push DATA SET

- 9. Key in data pattern on the key board (use AA to start)

- 10. R/W MODE: STATIC

- Probe the IC-pin with the data probe and check for the 1 or 0 LED as indicated in Figure 2. Repeat this step for each address and data line.

- 12. Repeat steps 6-11 using 5555 in step 7 and 55 in step 9.

#### Figure 2 Address and Data Lines

| Address and data lines | When writing 5555 pattern                                                                         |

|------------------------|---------------------------------------------------------------------------------------------------|

| IC-Pin                 | Logic State                                                                                       |

| B3-1                   | 0                                                                                                 |

| B3-3                   | 1                                                                                                 |

|                        | 0<br>1                                                                                            |

|                        |                                                                                                   |

|                        | 0                                                                                                 |

|                        | <b>1</b><br>0                                                                                     |

|                        | ĭ                                                                                                 |

|                        | 0                                                                                                 |

| B/C-5                  | 1                                                                                                 |

| B/C-7                  | 0                                                                                                 |

| B/C-9                  | 1                                                                                                 |

| B/C-18                 | 0                                                                                                 |

| B/C-16                 | 1                                                                                                 |

|                        | 0                                                                                                 |

|                        | 1                                                                                                 |

|                        | 0                                                                                                 |

|                        | 1                                                                                                 |

|                        | 0<br>1                                                                                            |

|                        | _                                                                                                 |

|                        | 0<br>1                                                                                            |

|                        | 0                                                                                                 |

|                        | 1                                                                                                 |

|                        | data lines IC-Pin B3-1 B3-3 B3-2 A/B-3 A/B-18 A/B-16 A/B-14 A/B-12 B/C-3 B/C-5 B/C-7 B/C-9 B/C-18 |

### C. RAM

1. Perform the CAT Box preliminary set-up.

- 2. Set the CAT Box switches as follows:

- a. Press TESTER RESET

- b. DBUS SOURCE: ADDR

- c. BYTES: 1024

- d. R/W MODE: (OFF)

- e. R/W: WRITE

- f. Enter 0000 on the keypad

- g. Toggle R/W MODE to PULSE and back to (OFF)

- h. R/W: READ

- i. Toggle R/W MODE to PULSE and back to (OFF)

- 3. If the CAT Box reads an address that doesn't compare, the COMPARE ERROR LED lights up, the ADDRESS/SIGNATURE display shows the failing address location, and the ERROR DATA DISPLAY switch is enabled. Using this switch, determine if the error is in the high- or low-order RAM.

- Repeat the test with DBUS SOURCE set to ADDR.

- 5. Repeat steps 2-4, entering 0400 on the keypad (step f).

- 6. Repeat steps 2-4, entering 2000 on the keypad (step f).

- 7. Repeat steps 2-4, entering 2400 on the keypai (step f).

- 8. Repeat steps 2-4, entering 2800 on the keypac (step f).

- 9. Repeat steps 2-4, entering 2C00 on the keypact (step f).

### D. Option Switch Inputs

- 1. Perform the CAT Box preliminary seque

- 2. BYTES: 1

- 3.  $R/\overline{W}$ : READ

- 4. R/W MODE: (OFF)

- 5. Key in *0D00*

- 6. R/₩ MODE: STATIC

- 7. Activate the option switches at location NIS while monitoring the DATA DISPLAY. The DATA DISPLAY will change if the switches are operating properly.

- 8. Repeat steps 4-7, entering 0E00 in step 5 and sectivate switches at location L12.

### E. Custom Audio I/O Chips

Unlike previous Atari coin-operated games, NOTE: Tempest™ has two custom audio I/O chips. Each must be tested separately.

- 1. Perform the CAT Box preliminary set-up.

- 2. BYTES: 1

- 3. R/W: WRITE

- 4. R/W MODE: (OFF) 5. Enter address from Figure 3

- 6. Press DATA SET

- 7. Enter the data from Figure 3 8. R/W MODE to PULSE and back to (OFF)

- 9. Repeat steps 5-8 for each address and data, not

- ing the test results.

### Figure 3 Custom Audio I/O Chips

| 60C2 55 AF Custom Audio I/O Chip #1 channel 2 produces pure tone.  60C3 00 Custom Audio I/O Chip #1 channel 2 off.  60C4 55 AF Custom Audio I/O Chip #1 channel 2 off.  60C5 00 Custom Audio I/O Chip #1 channel 2 off.  60C5 00 Custom Audio I/O Chip #1 channel 3 produces pure tone.  60C6 00 Custom Audio I/O Chip #1 channel 3 off.  60C6 55 AF Custom Audio I/O Chip #1 channel 3 off.  60C6 55 AF Custom Audio I/O Chip #1 channel 3 off.  60C6 55 AF Custom Audio I/O Chip #2 channel 3 off.  60C6 55 AF Custom Audio I/O Chip #2 channel 3 off.  60C6 55 AF Custom Audio I/O Chip #2 channel 3 off.  60C6 55 AF Custom Audio I/O Chip #2 channel 3 off.  60C6 55 AF Custom Audio I/O Chip #2 channel 4 produces pure tone.  60C7 00 Custom Audio I/O Chip #1 channel 4 produces pure tone.  60C7 00 Custom Audio I/O Chip #1 channel 4 off. | ADDRESS<br>60CF<br>60CF<br>60C0<br>60C1 | 00<br>03<br>55<br>AF | Custom Audio I/O Chip<br>#1 channel 1 produces<br>pure tone. | ADDRESS<br>60DF<br>60DF<br>60D0<br>60D1 | 00<br>03<br>55<br>AF | Custom Audio I/O Chip #2 channel 1 produces pure tone. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|--------------------------------------------------------------|-----------------------------------------|----------------------|--------------------------------------------------------|

| AF Custom Audio I/O Chip #1 channel 2 produces pure tone.  60C3  O Custom Audio I/O Chip #1 channel 2 off.  60D3  O Custom Audio I/O Chip #2 channel 2 produces pure tone.  60D3  O Custom Audio I/O Chip #2 channel 2 off.  60D4  60D5  AF Custom Audio I/O Chip #1 channel 3 produces pure tone.  60C5  O Custom Audio I/O Chip #1 channel 3 off.  60D6  60D7  AF Custom Audio I/O Chip #2 channel 3 off.  60D6  60D7  AF Custom Audio I/O Chip #2 channel 3 off.  60D6  60D7  AF Custom Audio I/O Chip #2 channel 3 off.  Custom Audio I/O Chip #2 channel 3 off.  60D6  60D7  AF Custom Audio I/O Chip #2 channel 4 produces pure tone.  60C7  O Custom Audio I/O Chip #2 channel 4 produces pure tone.  60D7  O Custom Audio I/O Chip                                                                                                           | ক্ত                                     | 00                   |                                                              | 60D1                                    | 00                   | •                                                      |

| #1 channel 2 off. #2 channel 2 off.  60C4 55 AF Custom Audio I/O Chip #1 channel 3 produces pure tone.  60C5 00 Custom Audio I/O Chip #1 channel 3 off.  60D6 55 60C7 AF Custom Audio I/O Chip #1 channel 4 produces pure tone.  #2 channel 2 off.  60D4 55 AF Custom Audio I/O Chip #2 channel 3 produces pure tone.  60D5 00 Custom Audio I/O Chip #2 channel 3 off.  60D6 55 60D7 AF Custom Audio I/O Chip #2 channel 4 produces pure tone.  60D7 00 Custom Audio I/O Chip #2 channel 4 produces pure tone.                                                                                                                                                                                                                                                                                                                                       |                                         |                      | #1 channel 2 produces                                        |                                         |                      | #2 channel 2 produces                                  |

| AF Custom Audio I/O Chip #1 channel 3 produces pure tone.  60C5  00 Custom Audio I/O Chip #1 channel 3 off.  60D5  60D5  AF Custom Audio I/O Chip #2 channel 3 produces pure tone.  60D5  00 Custom Audio I/O Chip #2 channel 3 off.  60D6  60D7  AF Custom Audio I/O Chip #1 channel 4 produces pure tone.  60C7  00 Custom Audio I/O Chip #2 channel 4 produces pure tone.  60D7  00 Custom Audio I/O Chip #2 channel 4 produces pure tone.                                                                                                                                                                                                                                                                                                                                                                                                        | (30 <b>(5</b> 3)                        | 00                   |                                                              | 60D3                                    | 00                   |                                                        |

| #1 channel 3 off. #2 channel 3 off.  60C6 55 60C7 AF Custom Audio I/O Chip #1 channel 4 produces pure tone.  60C7 00 Custom Audio I/O Chip 60D7 00 Custom Audio I/O Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |                      | #1 channel 3 produces                                        |                                         |                      | #2 channel 3 produces                                  |

| 60C7 AF Custom Audio I/O Chip #1 channel 4 produces pure tone.  60C7 AF Custom Audio I/O Chip #2 channel 4 produces pure tone.  60C7 00 Custom Audio I/O Chip 60D7 00 Custom Audio I/O Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60C5                                    | 00                   |                                                              | 60D5                                    | 00                   | ·                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |                      | #1 channel 4 produces                                        |                                         |                      | #2 channel 4 produces                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60C7                                    | 00                   |                                                              | 60D7                                    | 00                   |                                                        |

### F. Player Input Switches and Encoder Wheel

- 1. Perform the CAT Box Preliminary Set-up

- 2. DBUS SOURCE to DATA

- 3. BYTES: 256

- 4. RW: WRITE

- 5. R/W MODE: (OFF)

- 6. Key in 60D0

- 7. Press DATA SET

- 8. Key in 00

- 9. Toggle  $R/\overline{W}$  MODE to PULSE and back to (OFF)

- 10. BYTES: 1

- 11. R/W: READ

- 12. Key in 60D8

- 13. R/W MODE: STATIC

- 14. Pushing the following player input switches should cause the DATA DISPLAY to change: FIRE, SUPERZAPPER, 1-player start and 2-player start. (Also Player-2 FIRE and Player-2 SUPER-ZAPPER in cocktail\* games.)

NOTE: For the encoder wheel, repeat the above instructions keying in 60C0 in step 6 and 60C8 in step 12. Turning the encoder wheel should cause the DATA DISPLAY to change.

\*To test player-2 inputs in cocktail games connect IC D6-1 to +5.

### G. LED and Coin Counter Outputs

- 1. Perform the CAT Box Preliminary set-up.

- 2. DBUS SOURCE to DATA

- 3. BYTES: 1

- 4. R/W: WRITE

- 5. R/W MODE: (OFF)

- 6. Key in address from Figure 4

- 7. Press DATA SET

- 8. Key in on or off data from Figure 4

- 9. R/W MODE to STATIC and back to (OFF)

- 10. Repeat steps 6-9 to turn off coin counter solenoids, or to test another address.

If you write data that activates a solenoid, deactivate it by pressing the reset button on the game board or by writing "off" data. If you leave a solenoid activated for more than about 10 seconds it will overheat and may have to be replaced.

### F. Player Input Figure 4 LED and Coin Counter Addresses

| ADDRESS | ON-DATA | OFF-DATA | OUTPUT NAME         |

|---------|---------|----------|---------------------|

| 4000    | 01      | 00       | Right Coin Counter  |

| 4000    | 02      | 00       | Center Coin Counter |

| 4000    | 04      | 00       | Left Coin Counter   |

| 60E0    | FD      | FF       | 1-player start LED  |

| 60E0    | FE      | FF       | 2-player start LED  |

### H. Analog Vector-Generator

#### 1. Test:

- 1. Perform CAT Box preliminary set-up.

- 2. DATA SOURCE: DATA

- 3. R/W: WRITE

- 4. R/W MODE: (OFF)

- Key in address from Figure 5 or press AD-DRESS INC.

- 6. Press DATA SET

- 7. Key in data from Figure 5

- 8. Set R/W MODE to PULSE and then to (OFF

- 9. Repeat steps 5-8 for each address in Figure 1

#### CAUTION

You may damage the circuitry of the ximmonitor if you key in the VG GO signal without first checking all the addresses and data. Check the data by reading cach address location using steps 10-14

- 10. R/W: READ

- 11. R/W MODE: (OFF)

- 12. Key in address or press ADDRESS INC.

- 13. R/W MODE: PULSE

- 14. Check the data in the DATA DISTLAY egainst the data in Figure 5

If you are sure the data is correct, process to steps 15-19:

- 15. R/W MODE: WRITE

- 16. R/W: (OFF)

- 17. Key in VG GO address (4800 for TEMPESTIM

- 18. R/W to PULSE and then back to (OFF)

- 19. After writing to the VG GO address, the montor should show a large plus sign. Failure of the horizontal or vertical circuits shows the horizontal or vertical circuits shows the a single line drawn on the monitor of the volumenator does not display a large plus sign contact Atari Field Service.

Figure 5 Analog Vector-Generator Data

| Address | Data | Address | Data | Address | Data |

|---------|------|---------|------|---------|------|

| 2000    | 40   | 200C    | FF   | 2018    | 00   |

| 2001    | 80   | 200D    | 03   | 2019    | 40   |

| 2002    | 00   | 200E    | 00   | 201A    | 80   |

| 2003    | 70   | 200F    | 62   | 201B    | 00   |

| 2004    | 00   | 2010    | 40   | 201C    | 80   |

| 2005    | 1E   | 2011    | 80   | 201D    | 1F   |

| 2006    | 00   | 2012    | 80   | 201E    | 00   |

| 2007    | 1E   | 2013    | 00   | 201F    | 00   |

| 2008    | 00   | 2014    | 00   | 2020    | FF   |

| 2009    | 60   | 2015    | 00   | 2021    | 40   |

| 200A    | FF   | 2016    | 01   | 2022    | . 00 |

| 200B    | 03   | 2017    | 1F   | 2023    | E0   |

# 4

# Troubleshooting

With Signature Analysis

### Signature Analysis Set-up

- the CAT Box Preliminary set-up.

- 2 Some of the three BNC to E-Z clip cables (supplied with the CAT Box) to the SIGNATURE ANALYSIS CONTROL START, STOP and CLOCK tacks on the CAT Box.

- Attach the three black E-Z clips to a ground loop on the Tempest™ game PCB.

- 4) Attach the CAT Box data probe to the DATA jack on the CAT Box.

- 5 The colored E-Z clips on the cables will be moved about for each group of signatures to be taken.

The set-up for each group of signatures is located on the schematic sheet near the device to be checked. The signatures are located on or near the signal point on the schematic.

- 6. Set the CAT Box switches as follows:

- TESTER MODE: SIG

- TESTER SELF-TEST: OFF

- PULSE MODE: LATCHED

- START: As indicated

- STOP: As indicatedCLOCK: As indicated

- 7. Power up the game board and the CAT Box.

### B. Clock and Reset Circuitry

NOTE: For this test, remove W DOG DIS from GROUND.

#### 1. CAT Box Settings

| Probe | Trigger | - IC-Pin |

|-------|---------|----------|

| Start |         | A6-6     |

| Stop  |         | D3-8     |

| Clock | · J     | D3-8     |

#### 2. Signatures

| z. Olghalules                          |                        |                                      |

|----------------------------------------|------------------------|--------------------------------------|

| Logic Probe<br>on IC-Pin               | Signal<br>Name         | Signature<br>Should Be               |

| C4-3<br>C4-2<br>C4-6<br>C4-7           | 6MHz<br>3MHz<br>1.5MHz | 1730<br>3441<br>5CPA<br>36H3         |

| F3-6<br>F3-3<br>B4-8<br>B4-6           | E3MHz<br>E6MHz<br>3KHz | 3441<br>1730<br>7CUP<br>P74P         |

| D4-8<br>D4-6<br>D3-8<br>E4-15<br>E3-12 | RESET                  | 3214<br>C4P5<br>4668<br>F0F1<br>V990 |

### C. Address Lines

#### 1. CAT Box Settings for Address Bus Test

| Probe | Trigger | IC-Pin | Test Pt. |

|-------|---------|--------|----------|

| Start | 7_      | C2-25  |          |

| Stop  | ٦       | C2-25  |          |

| Clock | ī       | C2-39  | Ф2       |

### 2. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| B/C1-12     | AB0    | บบบบ      |

| B/C1-14     | AB1    | 5555      |

| B/C1-16     | AB2    | CCCC      |

| B/C1-18     | AB3    | 7F7F      |

| B/C1-9      | AB4    | 5H21      |

| B/C1-7      | AB5    | OAFA      |

| B/C1-5      | AB6    | UPFH      |

| B/C1-3      | AB7    | 52F8      |

| A/B1-12     | AB8    | HC89      |

| A/B1-14     | AB9    | 2H70      |

| A/B1-16     | AB10   | HPPC      |

| A/B1-18     | AB11   | 1293      |

| A/B1-3      | AB12   | HAP7      |

| B3-2        | A13    | 3C96      |

| B3-3        | A14    | 382/      |

| B3-1        | A15    | 7,55U     |

| A6-4        | A15    | (55)H     |

### D. Address Decoder

ग्वज्ञात्री।

### 1. CAT Box Settings for Address Decoder Test

|                        | ler Test | go 101 (d.   |

|------------------------|----------|--------------|

| Probe                  | Trigger  | IC-Pin       |

| Start<br>Stop<br>Clock | 777      | A6-3<br>A6-3 |

|                        |          |              |

|                        |          | • •          |

### 2. Signatures

**NOTE:** To obtain Signatures from IC J5, ground R/W testpoint.

|             | •      |           |

|-------------|--------|-----------|

| Logic Probe | Signal | Signature |

| on IC-Pin   | Name   | Should Be |

| B3-7        | 170    | F2A6      |

| E3-2        | 170    | F2A7      |

| F3-8        | EI/O   | F2A6      |

| J5-9        | VGRST  | 5969      |

| J5-10       | WDCLR  | 0PC5      |

| J5-11       | VGGO   | 270P      |

| J5-12       | BB*    | 9CH2      |

| B3-5        | VMEM   | 12U3      |

| B3-4        | AA*    | 4P0A      |

| J2-7        | ROM8   | 56C3      |

| J2-6        | ROM7   | 8019      |

| J2-5        | ROM6   | 5AH1      |

| J2-4        | ROM5   | 9HUC      |

| J2-9        | ROM4   | 1920      |

| J2-10       | ROM3   | C34C      |

| J2-11       | ROM2   | 597C      |

| J2-12       | ROM1   | UA87      |

| C1-7        | ROM0   | 4154      |

| C1-6        | ROMX   | 960F      |

|             |        |           |

# E ROM and Data

When taking signatures on ROMs, install a 270 pF capacitor between IC-Pin C2-23 and ground. This can be done in the socket at C2.

### CAT Box Settings for ROMX Test

| (III) |         |           |

|-------|---------|-----------|

| Probe | Trigger | Testpoint |

| Start |         | ROMX      |

| Stop  | Ţ       | ROMX      |

| Clock |         | ф2        |

| 10 PM |         |           |

#### 2. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| D1-9        | DB0    | 1F4H      |

| D1-10       | DB1    | 4P55      |

| D1-11       | DB2    | P2C5      |

| D1-13       | DB3    | UH32      |

| D1-14       | DB4    | 4HFA      |

| D1-15       | DB5    | 0P76      |

| D1-16       | DB6    | 86CP      |

| D1-17       | DB7    | P29C      |

### 3. CAT Box Settings for ROM0 Test (I.C. E1)

| (     |         |           |

|-------|---------|-----------|

| Probe | Trigger | Testpoint |

| Start |         | ROM0      |

| Stop  | J       | ROM0      |

| Clock |         | Ф2        |

#### 4. Signatures

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signatüre<br>Should Be |

|--------------------------|----------------|------------------------|

| E1-9                     | DB0            | 6481                   |

| E1-10                    | DB1            | P6A9                   |

| ⊨: E1-11                 | DB2            | 9552                   |

| E1-13                    | DB3            | 40F3                   |

| E1-14                    | DB4            | 37C2                   |

| E1-15                    | DB5            | 0A18                   |

| E1-16                    | DB6            | A2C0                   |

| E1-17                    | DB7            | 9HC5                   |

|                          |                |                        |

### 5. CAT Box Settings for ROM1 Test

| Trigger | Testpoint |

|---------|-----------|

|         | ROM1      |

|         | ROM1      |

| =_      | Ф2        |

|         | Trigger   |

#### 6. Signatures

| Signatures  |        |           |

|-------------|--------|-----------|

| Logic Probe | Signal | Signature |

| on IC-Pin   | Name   | Should Be |

| F1-9        | DB0    | 3892      |

| F1-10       | DB1    | 01U5      |

| F1-11       | DB2    | PH6P      |

| F1-13       | DB3    | UP9F      |

| F1-14       | DB4    | UP44      |

| F1-15       | DB5    | CA33      |

| F1-16       | DB6    | 3U05      |

| F1-17       | DB7    | 8CP3      |

### 7. CAT Box Settings for ROM2 Test 12. Signatures (I.C. H1)

| Probe                  | Trigger | Testpoint                 |

|------------------------|---------|---------------------------|

| Start<br>Stop<br>Clock | 7       | <u>ROM2</u><br>ROM2<br>ф2 |

#### 8. Signatures

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signature<br>Should Be |

|--------------------------|----------------|------------------------|

| H1-9                     | DB0            | T550                   |

| H1-10                    | DB1            | A01F                   |

| H1-11                    | DB2            | A540                   |

| H1-13                    | DB3            | 5U60                   |

| H1-14                    | DB4            | 2068                   |

| H1-15                    | DB5            | 9767                   |

| H1-16                    | DB6            | 54CA                   |

| H1-17                    | DB7            | 7F8F                   |

### 9. CAT Box Settings for ROM3 Test (I.C. J1)

| Probe | Trigger | Testpoint |

|-------|---------|-----------|

| Start |         | ROM3      |

| Stop  |         | ROM3      |

| Clock | 1_      | ф2        |

#### 10. Signatures

| 0. 0.5      | •      |           |  |

|-------------|--------|-----------|--|

| Logic Probe | Signal | Signature |  |

| on IC-Pin   | Name   | Should Be |  |

| J1-9        | DB0    | 09A6      |  |

| J1-10       | DB1    | 6A12      |  |

| J1-11       | DB2    | 91CA      |  |

| J1-13       | DB3    | 10HP      |  |

| J1-14       | DB4    | F53U      |  |

| J1-15       | DB5    | C67C      |  |

| J1-16       | DB6    | 8272      |  |

| 11.17       | DR7    | F651      |  |

#### 11. CAT Box Settings for ROM4 Test (I.C. K1)

| Probe                  | Trigger | Testpoint           |

|------------------------|---------|---------------------|

| Start<br>Stop<br>Clock |         | ROM4<br>ROM4<br>Ф 2 |

| Logic Probe             | Signal     | Signature    |

|-------------------------|------------|--------------|

| on IC-Pin               | Name       | Should Be    |

| K1-9                    | DB0        | A8FU         |

| K1-10                   | DB1        | U3U7         |

| K1-10<br>K1-11<br>K1-13 | DB2<br>DB3 | C8CH<br>353F |

| K1-14                   | DB4        | 93FU         |

| K1-15                   | DB5        | UFH1         |

| K1-16                   | DB6        | A165         |

| K1-17                   | DB7        | 5399         |

### 13. CAT Box Settings for ROM5 Test (I.C. L/M 1)

| <b>\</b> | •        |           |

|----------|----------|-----------|

| Probe    | Trigger  | Testpoint |

| Start    | <u>_</u> | ROM5      |

| Stop     | 1        |           |

| Clock    |          | Ф2        |

#### 14. Signatures

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| L/M1-9      | DB0    | 4876      |

| L/M1-10     | DB1    | 5397      |

| L/M1-11     | DB2    | 7396      |

| L/M1-13     | DB3    | C9CH      |

| L/M1-14     | DB4    | HF73      |

| L/M1-15     | DB5    | 11U6      |

| ĽM1-16      | DB6    | 43C8      |

| L/M1-17     | DB7    | 2R85      |

|             |        |           |

### 15. CAT Box Settings for ROM6 Test (I.C. M/N 1)

resipolitic

| Probe         | Trigge <b>r</b> |

|---------------|-----------------|

| Start         | 7_              |

| Stop<br>Clock |                 |

#### 16. Signatures

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signatur<br>Should Pt |

|--------------------------|----------------|-----------------------|

| M/N-9                    | DB0            | A4AC                  |

| M/N-10                   | DB1            | 3A7C                  |

| M/N-11                   | DB2            | 0F22                  |

| M/N-13                   | DB3            | H221                  |

| M/N-14                   | DB4            | 2H07                  |

| M/N-15                   | DB5            | 818A                  |

| M/N-16                   | DB6            | <b>*</b> 1699         |

| M/N-17                   | DB7            | 4149                  |

### 17. CAT Box Settings for ROM7 Test 22. Signatures (I.C. P1)

| Probe         | Trigger | Testpoint    |

|---------------|---------|--------------|

| Start         | 7_      | ROM7<br>ROM7 |

| Stop<br>Clock | _       | Ф2           |

#### 18. Signatures

| Logic Probe<br>on IC-Pin | Signal<br>Name | Signature<br>Should Be |

|--------------------------|----------------|------------------------|

| P1-9                     | DB0            | P4F3                   |

| P1-10                    | DB1            | 2C06                   |

| P1-11                    | DB2            | 4614                   |

| P1-13                    | DB3            | 7A63                   |

| P1-14                    | DB4            | 434C                   |

| P1-15                    | DB5            | 3C66                   |

| P1-16                    | DB6            | P8UC                   |

| P1-17                    | DB7            | 2C3A                   |

#### 19. CAT Box Settings for ROM8 Test (I.C. R1)

| Prope | irigger | iestpoint |

|-------|---------|-----------|

| Start |         | ROM8      |

| Stop  | ¯       | ROM8      |

| Clock | ī       | Ф2        |

|       | _       |           |

| 45    |         |           |

| 0 Signature        | s              |                        |

|--------------------|----------------|------------------------|

| ्रव्याः Probe      | Signal<br>Name | Signature<br>Should Be |

| EFFE A             | DB0<br>DB1     | 9HFP<br>U7HH           |

| 136-45-<br>136-46- | DB2<br>DB3     | F32H<br>F66U           |

| Brig.              | DB4<br>DB5     | U379<br>490P           |

|                    | DB6<br>DB7     | 5P99<br>CFA8           |

NOTE When taking signatures on IC N/P3, ground CIC-Pin B3-5.

#### CAT Box Settings for Vector POM Tost (IC N/P3)

| <b>ID</b> OIAL | 1621 /1.0 | . 14/1 0/ |           |

|----------------|-----------|-----------|-----------|

| Robe           | Trigger   | IC-Pin    | Testpoint |

| Sland          | ٦_        | N/P3-20   |           |

| Stop           |           | N/P3-20   |           |

| Clock          | 7         |           | Ф2        |

| Logic Probe | Signal | Signature |

|-------------|--------|-----------|

| on IC-Pin   | Name   | Should Be |

| N/P3-9      | DB0    | H1U9      |

| N/P3-10     | DB1    | 5U8C      |

| N/P3-11     | DB2    | 0C59      |

| N/P3-13     | DB3    | 507P      |

| N/P3-14     | DB4    | 2A8P      |

| N/P3-15     | DB5    | 9F0C      |

| N/P3-16     | DB6    | AH97      |

| N/P3-17     | DB7    | 29AH      |

NOTE: When taking signatures on I.C. R3, ground IC-Pin B3-5.

#### 23. CAT Box Settings for Vector ROM1 Test (I.C. R3)

| Probe | Trigger  | IC-Pin | Testpoint |

|-------|----------|--------|-----------|

| Start | <u>_</u> | R3-20  |           |

| Stop  |          | R3-20  |           |

| Clock | 7_       |        | Ф2        |

### 24. Signatures

| 4. Signatures |        |           |

|---------------|--------|-----------|

| Logic Probe   | Signal | Signature |

| on IC-Pin     | Name   | Should Be |

| R3-9          | DB0    | 3FH3      |

| R3-10         | DB1    | 0H59      |

| R3-11         | DB2    | 9H5H      |

| R3-13         | DB3    | 98PF      |

| R3-14         | DB4    | PA27      |

| R3-15         | DB5    | 5U3H      |

| R3-16         | DB6    | 97FC      |

| R3-17         | DB7    | 583A      |

### F. Math Box

The Math Box signature analysis procedure is somewhat different from other procedures, so follow these set-up instructions for the three tests carefully.

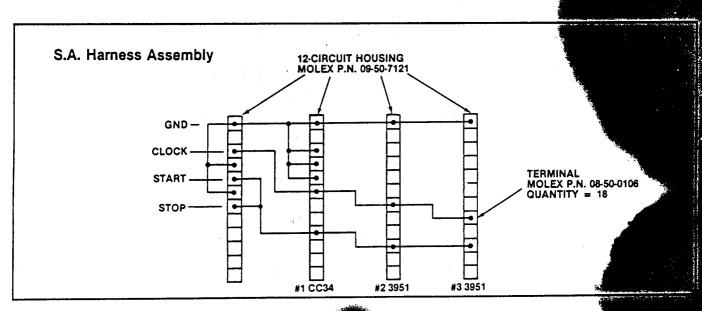

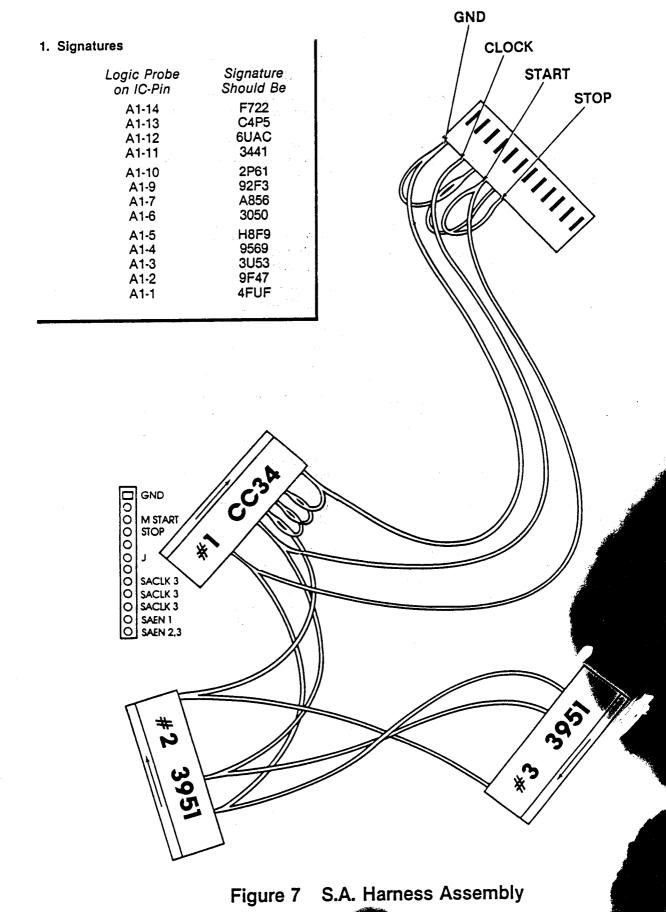

In addition to your CAT Box or signature analyzer, you'll need an SA Harness Assembly. Order Atari part number A036836-01 or see Figure 6 to make your own.

#### A. Math Box Test #1 Procedure:

- Plug SA Harness Assembly Test #1 connector onto Signature Analyzer connector (J16) on the Auxiliary PCB.

- 2. Connect the CAT Box Start, Stop and Clock E-Z hooks to the SA Harness Assembly as shown in Figure 7.

- On the main PCB, connect PWR ON RESET test point to ground, and power-up the game and the CAT Box.

- 4. Don't remove the microprocessor (6502A) from the main PCB.

Don't connect the 50 pin ribbon cable to the main PCB edge connector.

Don't connect W DOG DIS to ground.

- 5. Set the CAT Box switches as follows:

- a. START \_\_

- b. STOP \_\_\_

- d. TESTER MODE: SIG

- e. Press TESTER RESET

- 6. With the logic probe touching the +5V test point on the Auxiliary PCB, the ADDRESS/SIGNATURE display should read CC34. This will verify that your test set-up is correct. If you don't get CC34, recheck your set-up.

NOTE: Signatures are listed in the order that they should be done. As often as possible, *IC-Pin* refers to a chip output. As a general rule, when a bad signature is discovered, the IC listed in the *IC-Pin* column can be suspected as faulty.

Those signatures marked with an asterisk (\*) should be taken with a 1K resistor clipped between the logic probe and the +5V test point.

Figure 6 S.A. Harness Assembly

| Tempest*** Troubleshooting Guid       | e                            |                                                                                                                                                                                                                            |

|---------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Signatures  Logic Probe  on IC-Pin | Signature<br>Should Be       | F/H2-8 78AA*<br>J2-33 8638<br>J2-16 11C5*<br>J2-8 7U19*                                                                                                                                                                    |

| C1-11<br>C1-12<br>C1-13<br>C1-14      | H58A<br>77F7<br>85PA<br>7P25 | E2-34 A1F7<br>E2-31 1781<br>E2-16 9AFH*                                                                                                                                                                                    |

| D1-11<br>D1-12<br>D1-13<br>D1-14      | 5CP0<br>P5PH<br>725C<br>96PF | E5-11 C646  D4-8 0600  E4-11 CC34  F5-11 C835*  D4-6 C4U4                                                                                                                                                                  |

| F1-12<br>F1-11<br>F1-10<br>F1-9       | 4PPF<br>OUFO<br>3CAP<br>A6A3 | F5-6 753F<br>E4-8 CPU8<br>E5-8 45A1*                                                                                                                                                                                       |

| H1-12<br>H1-11<br>H1-10<br>H1-9       | 26A6<br>91HA<br>P9C1<br>2987 | B. Math Box Test #2A Procedure                                                                                                                                                                                             |

| J1-12<br>J1-11<br>J1-10<br>J1-9       | 96U0<br>UC59<br>6989<br>3FU4 | <ol> <li>Plug SA Harness Assembly Test #2 connector on-<br/>to Signature Analyzer connector (J16) on the Aux-<br/>iliary PCB.</li> </ol>                                                                                   |

| K1-12<br>K1-11<br>K1-10<br>K1-9       | 05A6<br>60H6<br>PPF6<br>34C2 | <ol> <li>Connect the CAT Box Start, Stop and Clock E-Z hooks to the SA Harness Assembly as shown in Figure 7.</li> <li>Don't remove the microprocessor (6502A) from</li> </ol>                                             |

| L1-12<br>L1-11<br>L1-10<br>L1-9       | 58A1<br>1AA2<br>F74F<br>6CF6 | the main PCB.  Don't connect the 50 pin ribbon cable to the main PCB edge connector.  Don't connect W DOG DIS to ground.  Don't connect PWR ON RESET to ground.                                                            |

| E1-12<br>E1-11<br>E1-10<br>E1-9       | F765<br>CPU8<br>0000<br>F515 | 4. Set the CAT Box switches as follows:  a. START  b. STOP  c. CLOCK  d. TESTER MODE: SIG                                                                                                                                  |

| E4-2<br>E4-6<br>A2-6<br>B1-2          | CC34<br>A6A3<br>0000<br>8A7H | e. Press TESTER RESET  5. Enter the self-test mode and advance the screen with the slam switch until the large rectangle ap-                                                                                               |

| B1-5<br>B1-6<br>B1-9                  | CU2P<br>1C6C<br>6U30         | <ul> <li>pears. This procedure is described in Figure 6,</li> <li>Chapter 2 of the Tempest<sup>™</sup> Operation, Maintenance, and Service Manual.</li> <li>6. With the logic probe touching the +5V test point</li> </ul> |

| B1-12<br>B1-15<br>B1-16               | 5AAH<br>03A7<br>9A08         | on the Auxiliary PCB, the ADDRESS/SIGNATURE display should read 3951. This will verify that your test set-up is correct. If you don't get 3951, recheck your set-up.                                                       |

| B1-19<br>K/L2-33<br>K/L2-16           | 2327<br>6PUP<br>9AFH*        | NOTE: Signatures are listed in the order that they should be done. As often as possible, <i>IC-Pin</i> refers to a chip output. As a general rule,                                                                         |

| K/L2-8<br>F/H2-33<br>F/H2-16          | 809A*<br>9CPP<br>11C5*       | when a bad signature is discovered, the IC listed in the IC-Pin column can be suspected as faulty.                                                                                                                         |

### B. Math Box Test #2B Procedure

- Plug SA Harness Assembly Test #2 connector onto Signature Analyzer connector (J16) on the Auxiliary PCB.

- Connect the CAT Box Start, Stop and Clock E-Z hooks to the SA Harness Assembly as shown in Figure 7.

- 3. Don't remove the microprocessor (6502A) from the main PCB.

Don't connect the 50 pin ribbon cable to the main PCB edge connector.

- Don't connect W DOG DIS to ground.

Don't connect PWR ON RESET to ground.

- 4. Set the CAT Box switches as follows:

a. START \_\_

- b. STOP \\_

c. CLOCK \_\_

d. TESTER MODE: SIG

- e. Press TESTER RESET

oter the self-test mode and advance the screet

- 5. Enter the self-test mode and advance the screen with the slam switch until the large rectangle approach. This procedure is described in Figure 6.

- pears. This procedure is described in Figure 6, Chapter 2 of the Tempest<sup>™</sup> Operation, Mainte-tnance, and Service Manual.

- With the logic probe touching the +5V test point on the Auxiliary PCB, the ADDRESS/SIGNATURE display should read 3951. This will verify that your

- (Asi set-up is correct. If you don't get 3951, reheckyour set-up.

- when a bad signature is discovered, the IC listed to the IC-Pin column can be suspect-

### े शिवसणक

| ⊮ogi€Probe | Signature |

|------------|-----------|

| ଜନୀC-Pin   | Should Be |

| C1-11      | 92F3      |

| C1-12      | A856      |

| C1-13      | 3050      |

| C1-14      | H8F9      |

| D1-11      | 9569      |

| D1-12      | 3U53      |

| D1-13      | 9F47      |

| D1-14      | 4FUF      |

### B. Math Box Test #3 Procedure

- 1. Plug SA Harness Assembly Test #3 connector onto Signature Analyzer connector (J16) on the Auxiliary PCB.

- Connect the CAT Box Start, Stop and Clock E-Z hooks to the SA Harness Assembly as shown in Figure 7.

- Don't remove the microprocessor (6502A) from the main PCB.

Don't connect the 50 pin ribbon cable to the main PCB edge connector.

Don't connect W DOG DIS to ground.

Don't connect PWR ON RESET to ground.

- 4. Set the CAT Box switches as follows:

- - c. CLOCK \_\_\_

d. TESTER MODE: SIG

e. Press TESTER RESET

check your set-up.

- Enter the self-test mode and advance the screen with the slam switch until the large rectangle appears. This procedure is described in Figure 6,

- Chapter 2 of the Tempest™ Operation, Maintenance, and Service Manual.

6. With the logic probe touching the +5V test point on the Auxiliary PCB, the ADDRESS/SIGNATURE display should read 3951. This will verify that your

- NOTE: Signatures are listed in the order that they should be done. As often as possible, *IC-Pin* refers to a chip output. As a general rule, when a bad signature is discovered, the IC listed in the *IC-Pin* column can be suspected as faulty.

Signature

test set-up is correct. If you don't get 3951, re-

### 1. Signatures

| on IC-Pin | Should Be |

|-----------|-----------|

| E2-22     | 1441      |

| E2-23     | 2883      |

| E2-24     | 5107      |

| E2-25     | A20P      |

| J2-22     | 441H      |

| J2-23     | 883A      |

| J2-24     | 1074      |

| J2-25     | 20P9      |

Logic Probe